4.2.2 Chuy n m ch kênhể ạ

Trong th c t hi n nay, có r t nhi u kĩ thu t chuy n m ch đang đ c ápự ế ệ ấ ề ậ ể ạ ượ

d ng. Trong đó, ph bi n nh t là kĩ thu t chuy n m ch kênh và kĩ thu t chuy nụ ổ ế ấ ậ ể ạ ậ ể

m ch gói. Nói chung vi c thi t k và ng d ng hai h th ng chuy n m ch nàyạ ệ ế ế ứ ụ ệ ố ể ạ

có nhi u đi m gi ng nhau.ề ể ố

Chuy n m ch kênh đ c đ nh nghĩa là kĩ thu t chuy n m ch đ m b oể ạ ượ ị ậ ể ạ ả ả

vi c thi t l p các đ ng truy n d n dành riêng cho vi c truy n tin c a m t quáệ ế ậ ườ ề ẫ ệ ề ủ ộ

trình trao đ i thông tin gi a hai hay nhi u thuê bao đi n tho i khác nhau. Chuy nổ ữ ề ệ ạ ể

m ch kênh đ c ng d ng cho vi c liên l c m t cách t c th i, quá trình chuy nạ ượ ứ ụ ệ ạ ộ ứ ờ ể

m ch đ c th c hi n nhanh chóng sao cho đ m b o th i gian th c v i đ trạ ượ ự ệ ả ả ờ ự ớ ộ ễ

th p (đ m b o tr t đ u cu i t i đ u cu i không v t quá ng ng 150ms). ấ ả ả ễ ừ ầ ố ớ ầ ố ượ ưỡ

Chuy n m ch kênh tín hi u s là quá trình k t n i, trao đ i thông tin cácể ạ ệ ố ế ố ổ

khe th i gian gi a m t s đo n c a tuy n truy n d n TDM s . Có hai c chờ ữ ộ ố ạ ủ ế ề ẫ ố ơ ế

th c hi n quá trình chuy n m ch kênh tín hi u s : C ch chuy n m ch khôngự ệ ể ạ ệ ố ơ ế ể ạ

gian s và c ch chuy n m ch th i gian s . Ph n ti p theo mô t nguyên t cố ơ ế ể ạ ờ ố ầ ế ả ắ

c u t o và ho t đ ng c a các t ng chuy n m ch theo c ch không gian cũngấ ạ ạ ộ ủ ầ ể ạ ơ ế

nh th i gian, trên c s đó, xây d ng tr ng chuy n m ch k t h p b o đ mư ờ ơ ở ự ườ ể ạ ế ợ ả ả

kích th c l n b t kỳ theo yêu c u.ướ ớ ấ ầ

4.2.2.1 T ng chuy n m ch không gian sầ ể ạ ố

T ng chuy n m ch không gian s S (Space Switch Stage) c u t o t m tầ ể ạ ố ấ ạ ừ ộ

ma tr n chuy n m ch kích th c N đ u vào và M đ u ra v t lý. L u ý r ng đâyậ ể ạ ướ ầ ầ ậ ư ằ

là h th ng TDM-s , do đó m i đ ng v t lý ch a n kênh th i gian mà chúngệ ố ố ỗ ườ ậ ứ ờ

mang các tín hi u PCM. Nh v y đ k t n i m t khe th i gian (TS-Time Slot)ệ ư ậ ể ế ố ộ ờ

b t kỳ nào trong m t đ ng PCM b t kỳ phía đ u vào c a ma tr n chuy n m chấ ộ ườ ấ ầ ủ ậ ể ạ

t i khe th i gian t ng ng (nghĩa là có cùng mã s TS) c a m t đ ng PCM b tớ ờ ươ ứ ố ủ ộ ườ ấ

kỳ phía đ u ra c a ma tr n thì m t đi m chuy n m ch thích h p c a ma tr nầ ủ ậ ộ ể ể ạ ợ ủ ậ

chuy n m ch c n ph i ho t đ ng trong su t th i gian c a TS đó và l p l i v iể ạ ầ ả ạ ộ ố ờ ủ ặ ạ ớ

chu kì T=125 micro giây trong su t quá trình t o kênh. Trong các th i gianố ạ ờ

khác,v n đi m chuy n m ch đó có th s d ng cho các quá trình n i khác.ẫ ể ể ạ ể ử ụ ố

T ng t nh v y đ i v i t t c các đi m chuy n m ch khác c a ma tr n cóươ ự ư ậ ố ớ ấ ả ể ể ạ ủ ậ

th đ c s d ng đ thi t l p kênh n i cho các cu c g i khác nhau.ể ượ ử ụ ể ế ậ ố ộ ọ

Chuy n m ch không gian tín hi u TDM-s th ng thi t l p đ ng th iể ạ ệ ố ườ ế ậ ồ ờ

m t s l ng l n các cu c n i qua ma tr n v i t c đ t c thì trong m t khungộ ố ượ ớ ộ ố ậ ớ ố ộ ứ ộ

tín hi u 125microsec, trong đó m i cu c n i t n t i trong th i gian c a m t kheệ ỗ ộ ố ồ ạ ờ ủ ộ

th i gian TS. M t cu c g i đi n tho i có th kéo dài trong kho ng th i gianờ ộ ộ ọ ệ ạ ể ả ờ

nhi u khung tín hi u PCM (thông th ng kho ng 1,2 - 2 tri u khung và t ngề ệ ườ ả ệ ươ

ng v i th i gian kho ng t 3 đ n 5 phút). Do v y c n có m t ki u đi u khi nứ ớ ờ ả ừ ế ậ ầ ộ ể ề ể

theo chu kì đ n gi n cho m i k t n i. Đi u này d dàng đ t đ c nh m t bơ ả ỗ ế ố ề ễ ạ ượ ờ ộ ộ

nh RAM đi u khi n c c b liên quan t i ma tr n chuy n m ch không gian.ớ ề ể ụ ộ ớ ậ ể ạ

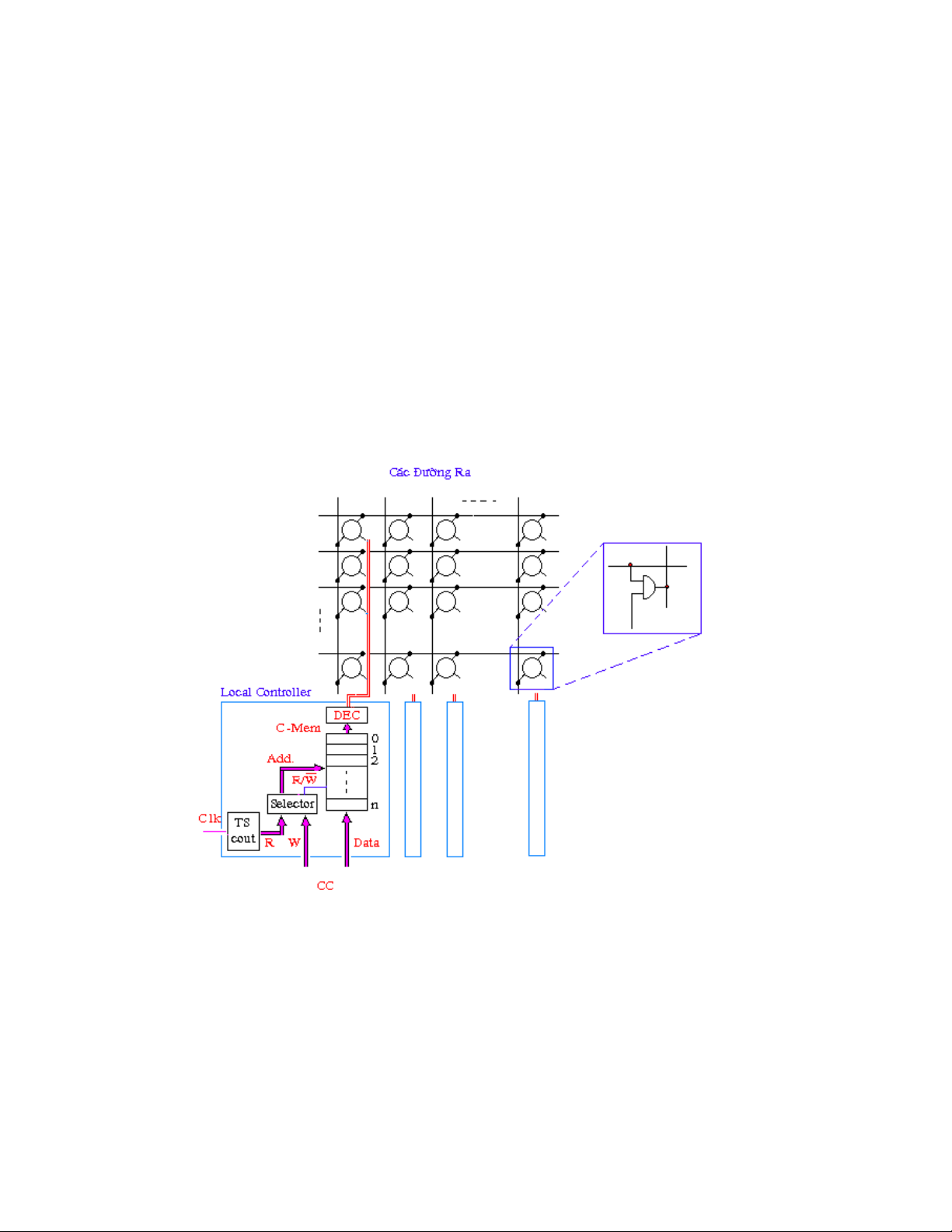

Hình 4.18 minh ho nguyên t c c u t o và ho t đ ng c a m t t ngạ ắ ấ ạ ạ ộ ủ ộ ầ

chuy n m ch không gian S. Chuy n m ch t ng S c u t o t 2 thành ph n cể ạ ể ạ ầ ấ ạ ừ ầ ơ

b n - Ma tr n chuy n m ch và kh i đi u khi n chuy n m ch c c b .ả ậ ể ạ ố ề ể ể ạ ụ ộ

Hình 4.18: Nguyên lý chuy n m ch t ng Sể ạ ầ

Ma tr n chuy n m ch vuông kích th c NxN, trong đó hàng dùng cho cácậ ể ạ ướ

đ ng PCM phía đ u vào và c t dùng cho các đ ng PCM phía đ u ra. T i giaoườ ầ ộ ườ ầ ạ

đi m c a hàng và c t đ u n i đi m chuy n m ch và thông th ng đó là c ngể ủ ộ ấ ố ể ể ạ ườ ổ

Các đ ngườ

vào

logic AND hay c ng logic ba tr ng thái. Chú ý r ng AND hay c ng logic ba tr ngổ ạ ằ ổ ạ

thái là m ch logic không nh , do v y chuy n m ch cho cùng m t khe th i gianạ ớ ậ ể ạ ộ ờ

gi a đ u vào và đ u ra c a ph n t chuy n m ch. Các đi m chuy n m ch trongữ ầ ầ ủ ầ ử ể ạ ể ể ạ

m i c t đ c đi u khi n b i m t b nh đi u khi n C-Mem (Control Memory).ỗ ộ ượ ề ể ở ộ ộ ớ ề ể

Kh i đi u khi n c c b bao g m b đ m khe th i gian TS-Counter, bố ề ể ụ ộ ồ ộ ế ờ ộ

ch n đ a ch Selector và b nh đi u khi n C-Mem đ th c hi n ch c năng đi uọ ị ỉ ộ ớ ề ể ể ự ệ ứ ề

khi n c c b ma tr n chuy n m ch. B nh C-Mem l u tr các s li u liên quanể ụ ộ ậ ể ạ ộ ớ ư ữ ố ệ

t i các đi m chuy n m ch t ng ng v i các khe th i gian TS trong khung tínớ ể ể ạ ươ ứ ớ ờ

hi u đã cho.ệ

Mã đ a ch nh phân đ c gán cho m i đi m chuy n m ch trong m t c t.ị ỉ ị ượ ỗ ể ể ạ ộ ộ

M i đ a ch thích h p sau đó s đ c s d ng đ ch n m t đi m chuy n m chỗ ị ỉ ợ ẽ ượ ử ụ ể ọ ộ ể ể ạ

yêu c u đ thi t l p cu c n i gi a m t đ u vào v i m t đ u ra c a ma tr nầ ể ế ậ ộ ố ữ ộ ầ ớ ộ ầ ủ ậ

chuy n m ch. Các đ a ch ch n này đ c nh trong b nh đi u khi n C-Memể ạ ị ỉ ọ ượ ớ ộ ớ ể ể

theo th t khe th i gian t ng ng v i bi u đ th i gian k t n i hi n th i. Nhứ ự ờ ươ ứ ớ ể ồ ờ ế ố ệ ờ ư

v y đ i v i c t 1, đ a ch c a đi m chuy n m ch s đ c thông m ch trong th iậ ố ớ ộ ị ỉ ủ ể ể ạ ẽ ượ ạ ờ

gian TS#0 s đ c nh trong ô nh có đ a ch 0 c a C-Mem cho c t, đ a ch c aẽ ượ ớ ớ ị ỉ ủ ộ ị ỉ ủ

đi m chuy n m ch s thông m ch trong khe th i gian TS#1 s đ c nh trong ôể ể ạ ẽ ạ ờ ẽ ượ ớ

nh đ a ch 1. T ng t nh v y đ i v i t t c các đ a ch khác trong t ngớ ị ỉ ươ ự ư ậ ố ớ ấ ả ị ỉ ầ

chuy n m ch.ể ạ

T hình 4.18 ta có th nh n th y r ng m i C-Mem ch đi u khi n m từ ể ậ ấ ằ ỗ ỉ ề ể ộ

c t c a ma tr n, cách s p x p nh th này g i là đi u khi n đ u ra. T t nhiênộ ủ ậ ắ ế ư ế ọ ề ể ầ ấ

cũng có th s p x p đi u khi n theo đ u vào (đi u khi n theo hàng c a maể ắ ế ề ể ầ ề ể ủ

tr n).ậ

Đ n m v ng b n ch t c a v n đ trên c s lý thuy t đã trình bày,ể ắ ữ ả ấ ủ ấ ề ơ ở ế

ph n ti p theo mô t nguyên t c ho t đ ng chuy n m ch kênh c a t ng S. Đầ ế ả ắ ạ ộ ể ạ ủ ầ ể

cho vi c miêu t đ c hoàn toàn xác đ nh chúng ta hãy kh o sát m t ví d c thệ ả ượ ị ả ộ ụ ụ ể

mô t ho t đ ng c a t ng S ph c v cho m t cu c n i gi a TS#0 c a lu ng tínả ạ ộ ủ ầ ụ ụ ộ ộ ố ữ ủ ồ

hi u PCM1 đ u vào v i TS#0 c a lu ng tín hi u PCM1 phía đ u ra. ệ ầ ớ ủ ồ ệ ầ

Căn c vào yêu c u chuy n m ch c th đã cho, tr c h t h th ng đi uứ ầ ể ạ ụ ể ướ ế ệ ố ề

khi n trung tâm CC (Central Control) c a t ng đài c a s t o các s li u đi uể ủ ổ ủ ẽ ạ ố ệ ề

khi n đ n p vào b nh C-Mem c a t ng S. T hình 4.18, rõ ràng đi m chuy nể ể ạ ộ ớ ủ ầ ừ ể ể

m ch duy nh t có th đ m b o cho yêu c u k t n i PCM1 phía đ u vào v iạ ấ ể ả ả ầ ế ố ầ ớ

PCM1 phía đ u ra là ANDầ11 do đó CC t o mã đ a ch nh phân cho ph n t ANDạ ị ỉ ị ầ ử 11

này. Vì theo yêu c u ph i th c hi n chuy n m ch cho khe th i gian TS#0 do v yầ ả ự ệ ể ạ ờ ậ

CC s chi m ô nh có đ a ch mã nh phân 0 t ng ng c a C-Mem. Các s li uẽ ế ớ ị ỉ ị ươ ứ ủ ố ệ

c b n đã có CC n p đ a ch nh phân AND11 vào ô nh 0 c a C-Mem t ng S,ơ ả ạ ị ỉ ị ớ ủ ầ

xong nó giao quy n đi u khi n cho kh i đi u khi n c c b đi u khi n tr c ti pề ề ể ố ề ể ụ ộ ề ể ự ế

quá trình ti p theo.ế

Nh th , khi b t đ u m t khung tín hi u PCM tín hi u đ ng h th nh tư ế ắ ầ ộ ệ ệ ồ ồ ứ ấ

tác đ ng vào b đ m khe th i gian TS-Counter làm cho b đ m này thi t l pộ ộ ế ờ ộ ế ế ậ

tr ng thái 0 có mã nh phân t ng ng v i đ a ch ô nh 0 c a C-Mem, nh bạ ị ươ ứ ớ ị ỉ ớ ủ ờ ộ

ch n đ a ch Selector mã tr ng thái này đ c đ a t i BUS đ a ch c a b nh C-ọ ị ỉ ạ ượ ư ớ ị ỉ ủ ộ ớ

Mem. Đ ng th i v i vi c t o mã đ a ch , Selector t o ra tín hi u đi u khi n đ cồ ờ ớ ệ ạ ị ỉ ạ ệ ề ể ọ

đ a t i C-Mem do đó n i dung ch a trong ô nh 0 đ c đ a ra thanh ghi-gi i mã.ư ớ ộ ứ ớ ượ ư ả

Vì n i dung này l i chính là đ a ch c a ph n t chuy n m ch AND11, do đó đãộ ạ ị ỉ ủ ầ ử ể ạ

t o đ c tín hi u đi u khi n đi m chuy n m ch này, nh đó tín hi u PCM ch aạ ượ ệ ề ể ể ể ạ ờ ệ ứ

trong khe th i gian TS#0 c a PCM1 phía đ u vào đ c chuy n qua ph n tờ ủ ầ ượ ể ầ ử

chuy n m ch AND11 đ h ng t i PCM1 phía đ u ra c a ma tr n chuy nể ạ ể ướ ớ ở ầ ủ ậ ể

m ch S, t c là đã th c hi n ch c năng chuy n m ch.ạ ứ ự ệ ứ ể ạ

K t thúc th i gian c a TS#0, xung đ ng h th 2 tác đ ng vào TS-ế ờ ủ ồ ồ ứ ộ

Counter làm nó chuy n sang tr ng thái 1 có mã nh phân t ng ng v i đ a ch ôể ạ ị ươ ứ ớ ị ỉ

nh 1 c a C-Mem. Nh v y k t thúc vi c t o tín hi u đi u khi n cho AND11ớ ủ ư ậ ế ệ ạ ệ ề ể

đ i v i quá trình chuy n m ch cho TS#0 theo yêu c u. T ng t nh v y đ iố ớ ể ạ ầ ươ ự ư ậ ố

v i các khe th i gian ti p theo và th t c đ c l p l i v i chu kì T = 125microớ ờ ế ủ ụ ượ ặ ạ ớ

giây trong su t quá trình thi t l p n i cho cu c g i đang xét.ố ế ậ ố ộ ọ

Khi cu c g i k t thúc CC nh n bi t và nó s gi i phóng cu c n i m tộ ọ ế ậ ế ẽ ả ộ ố ộ

cách đ n gi n b ng ho t đ ng xoá s li u đã ghi vào C-Mem nh đã nêu khi b tơ ả ằ ạ ộ ố ệ ư ắ

đ u cu c g i. Trong các t ng chuy n m ch S th c t , các bít tín hi u PCMầ ộ ọ ầ ể ạ ự ế ệ

th ng đ c ghép kênh t o lu ng t c đ cao và bi n đ i thành d ng song songườ ượ ạ ồ ố ộ ế ổ ạ

tr c khi qua t ng S. ướ ầ

4.2.2.2 T ng chuy n m ch th i gian s ầ ể ạ ờ ố

Nh đã th y ph n 4.2.2.1, c u t o và ho t đ ng c a chuy n m ch t ngư ấ ở ầ ấ ạ ạ ộ ủ ể ạ ầ

S ch th c hi n cho các quá trình chuy n m ch có cùng ch s khe th i gian g aỉ ự ệ ể ạ ỉ ố ờ ữ

đ ng PCM vào và đ ng PCM ra. Trong tr ng h p t ng quát có yêu c u traoườ ườ ườ ợ ổ ầ

đ i khe th i gian gi a đ u vào và đ u ra khác nhau thìs ph i ng d ng t ngổ ờ ữ ầ ầ ả ứ ụ ầ

chuy n m ch th i gian T (Time Switch Stage).ể ạ ờ

Hình 4.19: Trao đ i khe th i gianổ ờ

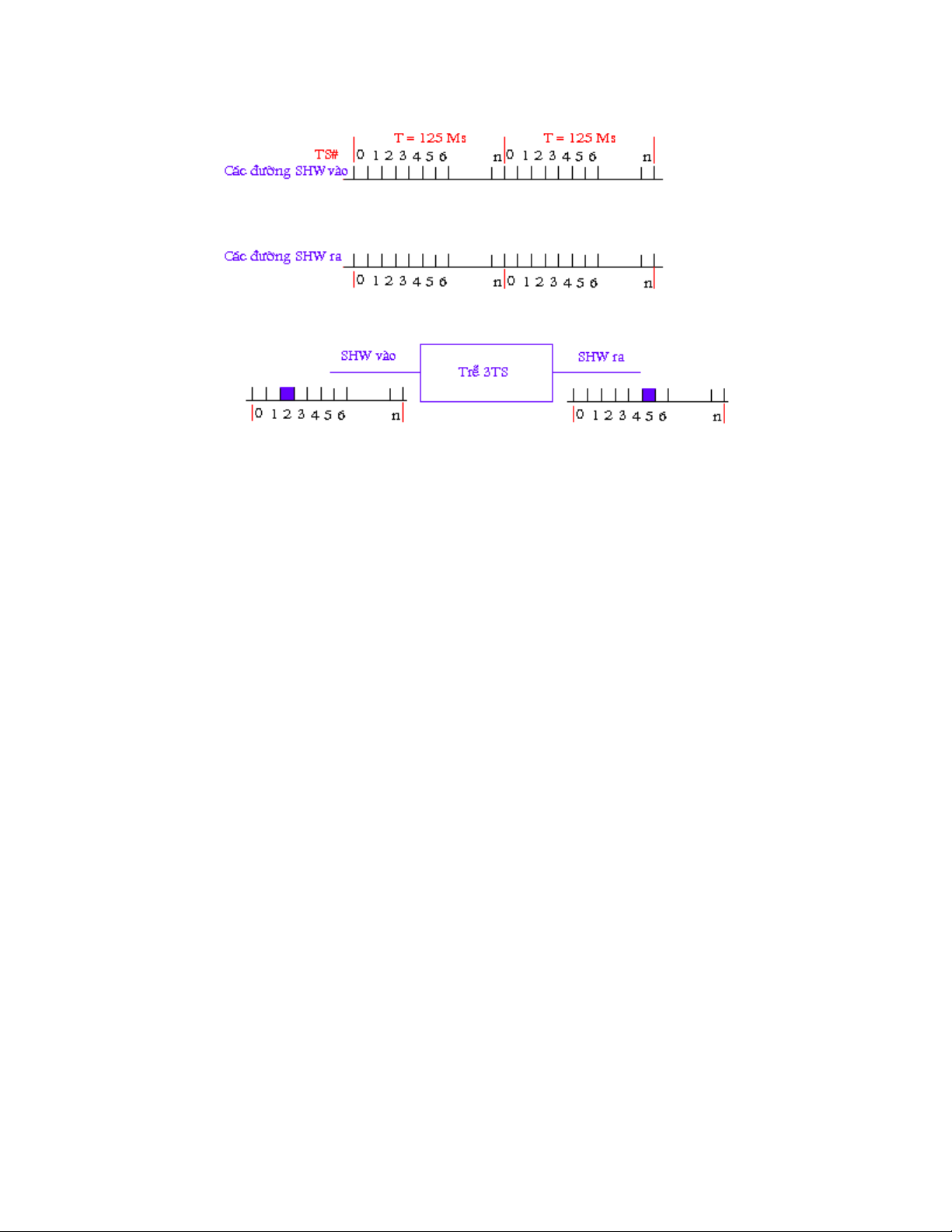

Hình 4.19 minh ho quá trình trao đ i khe th i gian gi a TS#2 và TS#5ạ ổ ờ ữ

cho hai khung liên ti p nhau gi a đ ng PCM vào và PCM ra c a t ng chuy nế ữ ườ ủ ầ ể

m ch T.ạ

Vì các khe th i gian TS đ c s p x p liên ti p nhau theo th t tăng d nờ ượ ắ ế ế ứ ự ầ

do v y đ trao đ i thông tin gi a các khe th i gian TS#2 và TS#5, tín hi u PCMậ ể ổ ữ ờ ệ

trong TS#2 c n ph i đ c l u t m th i t i t ng T trong kho ng th i gian 5-2 =ầ ả ượ ư ạ ờ ạ ầ ả ờ

3TS trong cùng m t khung, sau đó vào khe th i gian c a TS#5, tín hi u PCM nàyộ ờ ủ ệ

đ c đ a ra đ ng PCM phía đ u ra c a t ng chuy n m ch.ượ ư ườ ầ ủ ầ ể ạ

Tr ng h p n u c n chuy n m ch gi a khe th i gian đ u ra v i kheườ ợ ế ầ ể ạ ữ ờ ở ầ ớ

th i gian có ch s l n h n phía đ u vào, ví d TS#6 và TS#2 nh minh hoờ ỉ ố ớ ơ ở ầ ụ ư ạ

trên Hình 4.20 thì tín hi u không th tr trong cùng m t khung mà ph i tr sangệ ể ễ ộ ả ễ

khung ti p sau. C th là (N-6) + 2 khe th i gian, trong đó N là s khe th i gianế ụ ể ờ ố ờ

trong khung PCM, đây N = n+1 = 32.ở

![PROFIBUS và mạng truyền thông: Tổng quan, ứng dụng [Năm hiện tại]](https://cdn.tailieu.vn/images/document/thumbnail/2019/20191208/camtucau99/135x160/9551575800543.jpg)

![Trắc nghiệm Mạch điện: Tổng hợp câu hỏi và bài tập [năm hiện tại]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251118/trungkiendt9/135x160/61371763448593.jpg)