92

TẠP CHÍ KHOA HỌC VÀ CÔNG NGHỆ Trần Duy Hưng và ctv.

*Email: nvtruong.25890@gmail.com

TẠP CHÍ KHOA HỌC VÀ CÔNG NGHỆ

TRƯỜNG ĐẠI HỌC HÙNG VƯƠNG

Tập 35, Số 2 (2024): 92 - 100

JOURNAL OF SCIENCE AND TECHNOLOGY

HUNG VUONG UNIVERSITY

Vol. 35, No. 2 (2024): 92 - 100

Email: tapchikhoahoc@hvu.edu.vn Website: www.jst.hvu.edu.vn

PHƯƠNG PHÁP KHỐNG CHẾ VÀ KIỂM TRA CHÂN FPGA

DỰA TRÊN TIÊU CHUẨN IEEE 1149.1 VÀ XJLINK

Trần Duy Hưng1, Bùi Hoàng Tùng1, Nguyễn Văn Trường1*, Chu Ngọc Hải1

1Trường Cao đẳng Công nghiệp Quốc phòng, Phú Thọ

Ngày nhận bài: 19/3/2024; Ngày chỉnh sửa: 04/6/2024; Ngày duyệt đăng: 10/6/2024

DOI: https://doi.org/10.59775/1859-3968.188

Tóm tắt

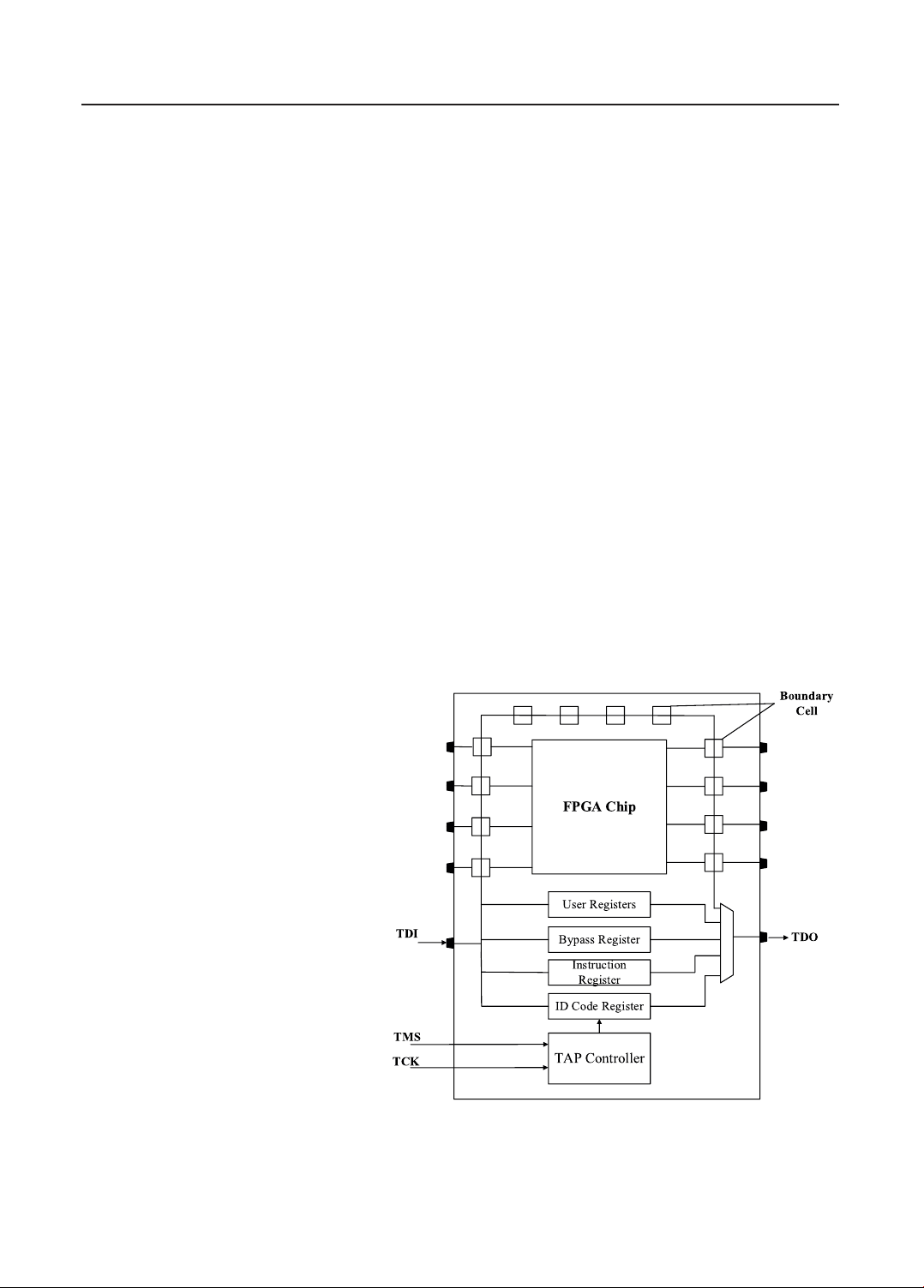

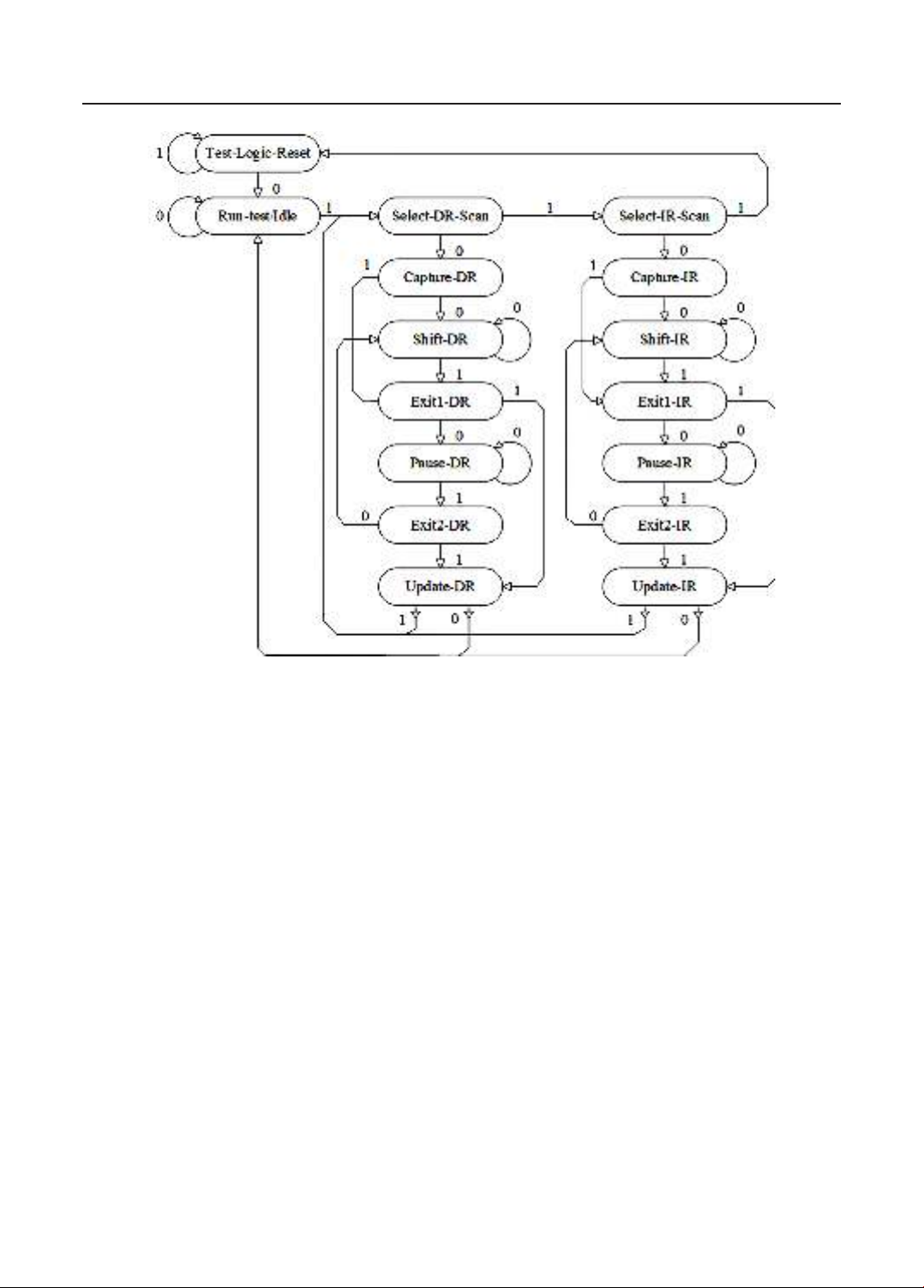

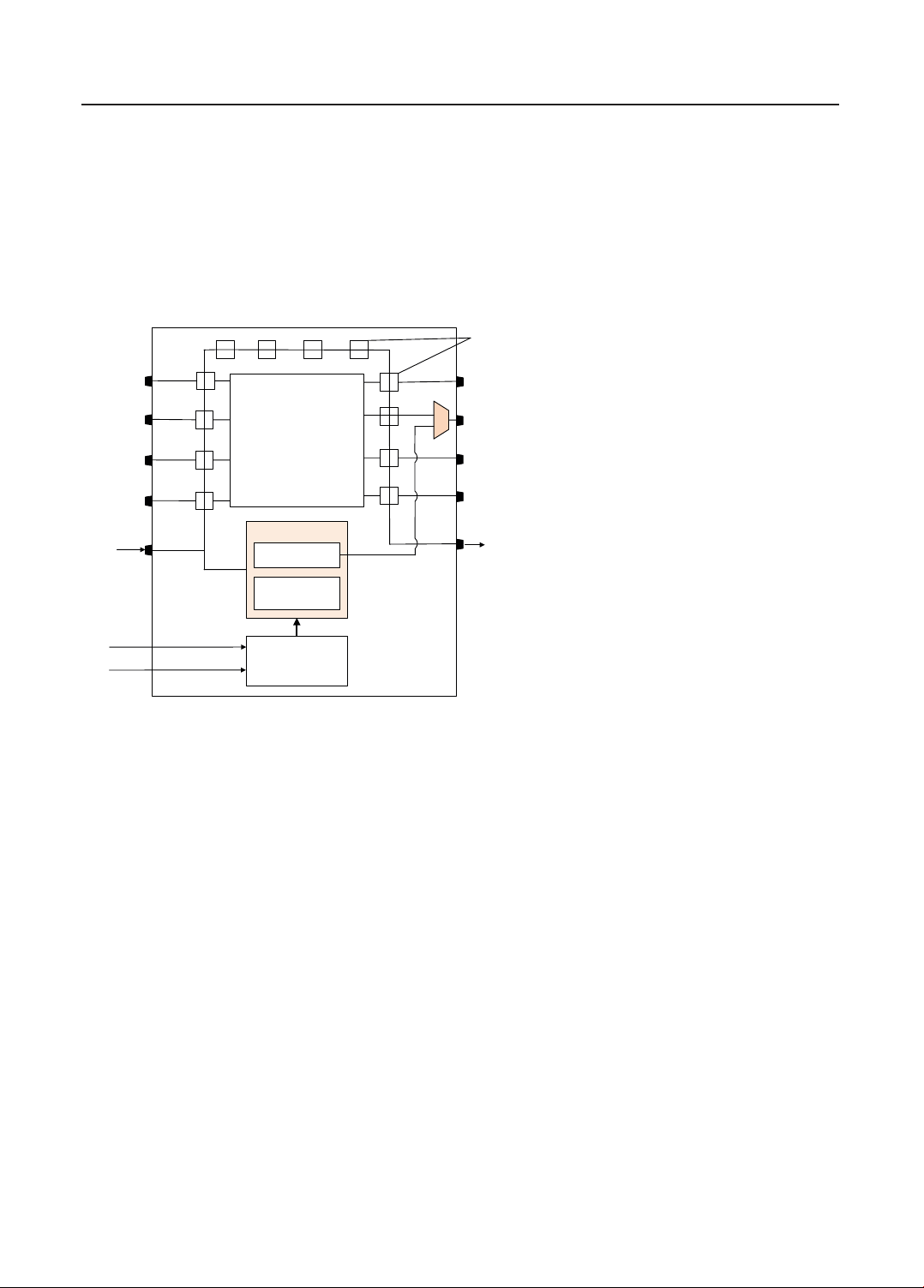

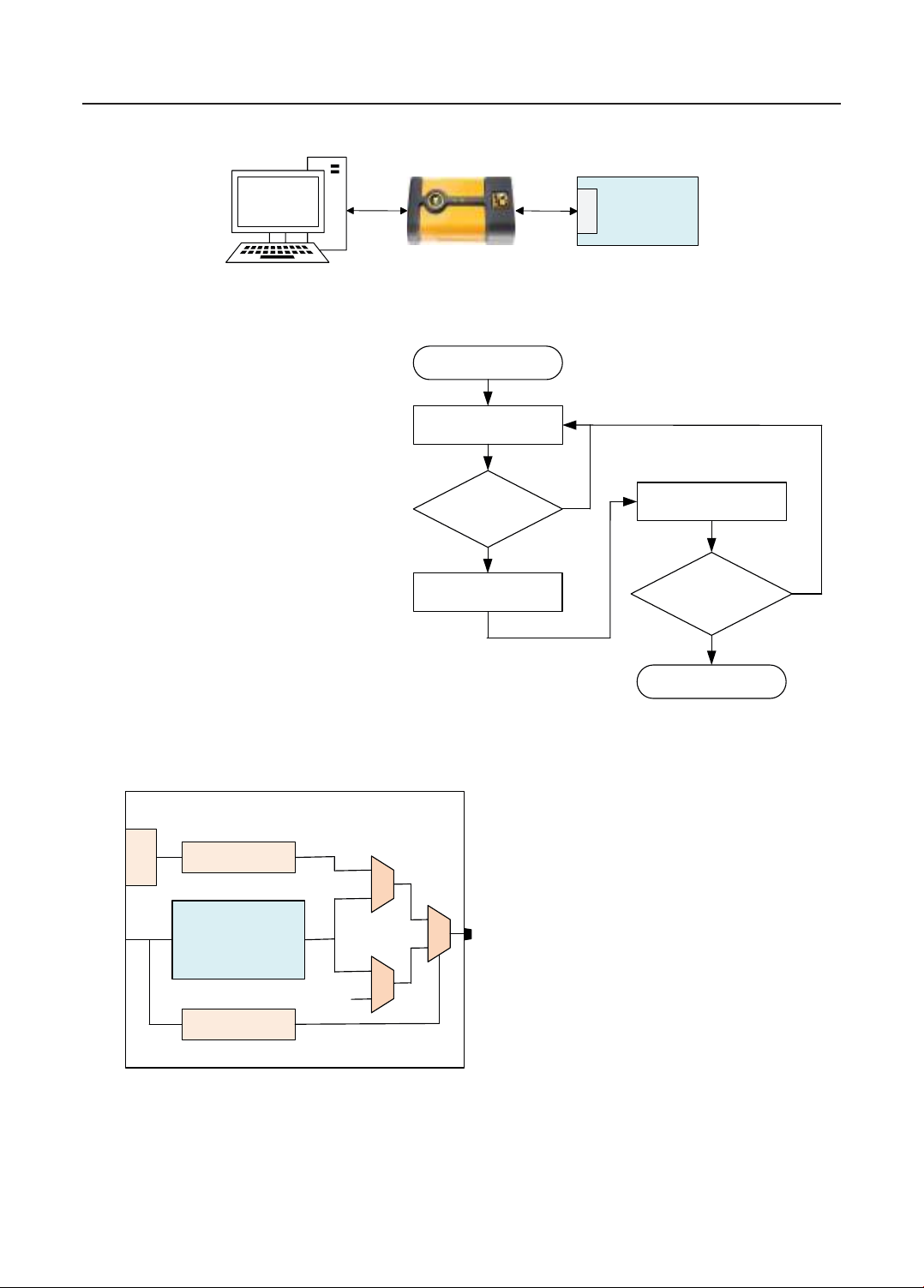

Trong bài viết này, chúng tôi đề xuất một phương pháp khống chế và kiểm tra khả năng hoạt động của các

chân chip FPGA khi đang hoạt động trong hệ thống điện điện tử dựa trên tiêu chuẩn IEEE 1149.1. Phương

pháp sử dụng phần cứng XJLink thông qua nhân IP theo kết cấu quét biên tiêu chuẩn IEEE 1149.1 tích hợp bên

trong FPGA thực hiện khống chế và gài lỗi trên một số chân của chip để kiểm tra tính năng của các chân đó mà

không cần thực hiện các tác động vật lý hay phải tháo dỡ FPGA ra khỏi bo mạch. Kết quả thực nghiệm trên các

bo mạch Xilinx FPGA cho thấy, phương pháp đề xuất có độ tin cậy và tính linh hoạt cao, tốc độ khống chế nhanh

nhất lên tới 150MHz trong khi các chân khác của chip vẫn hoạt động bình thường. Đồng thời, phương pháp đề

xuất còn có thể thực hiện khống chế ngay sau khi FPGA được cấp nguồn.

Từ khóa: Công nghệ kiểm tra quét biên, tiêu chuẩn IEEE 1149.1, cổng JTAG, gài lỗi, Xilinx FPGA.

1. Đặt vấn đề

Trong những năm gần đây, công nghệ bán

dẫn phát triển giúp cho các vi xử lý như mảng

cổng lập trình được dạng trường FPGA, bộ

xử lý tín hiệu DSP, vi xử lý ARM ngày càng

nhỏ gọn, mật độ chân nhiều đem đến thách

thức lớn cho lĩnh vực kiểm tra, đảm bảo tính

chính xác trong quá trình hoạt động của các

chip. Đặc biệt là trong một số lĩnh vực đặc

thù như các thiết bị máy bay, tàu ngầm quân

sự, yêu cầu rất cao về tính hoạt động chính

xác, không xảy ra sự cố, trong trường hợp

xảy ra sự cố phải cần có biện pháp phát hiện

và khắc phục ngay lập tức để đảm bảo an

toàn cho người và thiết bị.

Phương pháp sử dụng phần mềm khống

chế và gài lỗi sai khác nhau vào các chân

của chip từ đó đánh giá chất lượng của chân

được gài là phương pháp phổ biến hiện nay.

Trong bài viết của tác giả Le đã phân tích

sâu về ứng dụng và thách thức của phương

pháp gài lỗi trong các hệ thống ảo [1]. Một

số kết quả tiêu biểu sử dụng phương pháp

gài lỗi kiểm tra và khống chế chân chip như:

Bộ gài lỗi tại các nút mạch số và mạch tương

tự thông qua đầu dò do Qin Haibo đề xuất