BÀI

6

Tên

bài:

HO T Đ NG NG TẠ Ộ Ắ (Interrupt)

GI

Ớ

I

THI UỆ

Bài

này

trình

bày

về

khả

năng

quản

lý

đ ngồ

th

iờ

nhi uề

thiế

t

bị

ngo iạ

vi

nhờ

vào

tính

năng

xử

lý

ngắ

t

c aủ

MCS-51,

đi uề

này

rấ

t

phù

h pợ

v iớ

yêu

c uầ

l pậ

trình

hưngớ

đi uề

khi n N iể ộ

dung

bài

g mồ

cả

lý

thuyế

t

và

th

ực

hành

trên

bộ

th

ực

t

pậ

UNIKIT, t

hiế

t

bị

ngo iạ

vi

có

th

ể

giao

ti

pế

v iớ

8051

thông

qua

các

ngỏ

I/O

đ cượ

trang

bị

s nẳ

t

rên

board

UNIKIT

như

:

Công

t

ắ

c,

nút

nhấ

n,

đèn,

chuôn

g,

đ ngộ

cơ

...

M CỤ

TIÊU

TH CỰ

HI NỆ

•Hi uể

đ cượ

t

ác

d ngụ

th

ực

t

ế

của

mộ

t

hệ

th

ngố

đ cượ

đi uề

khi nể

b ngằ

tí

n

hi uệ

ngắ

t.

•Biế

t

đ cượ

t

ổ

chức

ngắ

t

và

cơ

chế

th

ực

hi nệ

chưngơ

trìn

h

ph cụ

vụ

ngắ

t

c aủ

8051

•Biế

t

cách

kh iở

t

oạ

ngắ

t t

heo

yêu

cầ

u.

NỘ

I

DUNG

CHÍNH

N iộ

dung

bài

h cọ

t

pậ

trung

về

các

chủ

đề

chính

như

sau:

•Vai

trò

c aủ

ngắ

t

trong

yêu

c uầ

đi uề

khi nể

•

T

ổ

chức

ngắ

t

trong

8051

•Các

thanh

ghi

chức

năng

đ cặ

biệ

t

liên

quan

•Phưngơ

pháp

kh iở

t

oạ

ngắ

t

•Cách

viế

t

chưngơ

trình

ph cụ

vụ

ngắ

t

kích

th

ưcớ

nhỏ

và

l nớ

•Các

ứng

dụng

đi nể

hình

1

1.

MỞ

Đ UẦ

Ngắ

t

là

sự

xuấ

t

hi nệ

c aủ

mộ

t

đi uề

kiệ

n,

mộ

t

sự

ki nệ

làm

t

mạ

dừng

chưngơ

trình

trong

khi

đi uề

ki nệ

này

đ cượ

ph cụ

vụ

bở

I

mộ

t

chưngơ

trì

nh

khác.

Ngắ

t

có

mộ

t

vai

trò quan

tr

ngọ

trong

thiế

t

kế

và

th

ực

hi nệ

các

ứng

d ngụ

c aủ

vi

đi uề

khiể

n.

Chúng

cho

phép

hệ

th

ngố

đáp

ứng

không

đ ngồ

bộ

vớ

I

mộ

t

sự

ki nệ

và

xử

lý

sự

ki nệ

trong

khi

mộ

t

chưngơ

trình

khác

đang

hoạ

t

đ ng.ộ

Mộ

t

hệ

th

ngố

đ cượ

đi uề

khi nể

b ngằ

ngắ

t t

oạ

mộ

t

oả

giác

th

ực

hi nệ

đ ngồ

th

ờ

I

nhi uề

công

vi cệ

cùng

mộ

t

lúc..

Dỉ

nhiên,

t

ạ

I

mộ

t th

ờ

I

đi mễ

CPU

không

th

ể

th

ực

hi nệ

nhi uề

h nơ

mộ

t

l nhệ

nhưng

nó

có

th

ể

t

mạ

dừng

chưngơ

trìn

h

để

th

ực

hi nệ

mộ

t

chưngơ

trình

khác

và

sau

đó

tr

ở

lạ

I

chưngơ

trình

đ uầ

tiên.

Đi mễ

khác

là

trong

mộ

t

hệ

th

ngố

đi uề

khi nể

b ngằ

ngắ

t,

các

ngắ

t

không

x yả

ra

như

là

kế

t

quả

c aủ

mộ

t

l nhệ

(như

l nhệ

gọ

I

chưngơ

trình

con)

mà

là

đáp

ứng

vớ

I

mộ

t

sự

ki nệ

x yả

ra

mộ

t

cách

không

đ ngồ

bộ

vớ

I

chưngơ

trìn

h

chính

có

nghĩa

là

không

biế

t tr

ưcớ

chưngơ

trìn

h

chính

sẻ

bị

ngắ

t

lúc

nà

o.

Chưngơ

trình

xử

lý

ngắ

t

đ cượ

gọ

I

là

chưngơ

trình

ph cụ

vụ

ngắ

t

(Interrupt

service

routine)

viế

t t

ắ

t

là

ISR

hay

qu nả

lý

ngắ

t. ISR

hoạ

t

đ ngộ

để

đáp

ứng

mộ

t

ngắ

t

và

t

hưngờ

th

ực

hi nệ

mộ

t

thao

tác

vào

ho cặ

ra

đ nế

mộ

t

thiế

t

bị

.

Khi

xảy

ra

mộ

t

ngắ

t thì

chưngơ

trình

chính

t

mạ

t

hờ

I

dừng

lạ

I

và

rẻ

nhánh

đ nế

ISR. IS

R

th

ực

hi nệ

các

thao

tác

c nầ

thiế

t

và

kế

t

thúc

vớ

I

l nhệ

tr

ở

về

t

ừ

ngắ

t

và

chưngơ

trình

chính

lạ

I ti

pế

t

cụ

t

ừ

n iơ

t

mạ

dừng.

Như

vậy

có

th

ể

nói

chưngơ

trình

chính

hoạ

t

đ ngộ

ở

mức

cơ

sở

và

các

ISR

hoạ

t

đ ngộ

ở

mức

ngắ

t

cũng

có

dùng

các

thuậ

t

ngữ

:

“phía

tr

ưc”ớ

(foreground)

để

chỉ

mức

cơ

sở

và

“ph

ía

sau”

(backgrround)

để

chỉ

mức

ngắ

t,

trong

hình

6.1a

trình

bày

hoạ

t

đ ngộ

c aủ

mộ

t

chưngơ

trình

không

có

ngắ

t

và

6.1b

là

hoạ

t

đ ngộ

c aủ

chưngơ

trình

chính

ở

mức

cơ

sở

có

ngắ

t

và

các

ngắ

t

hoạ

t

động

ở

mức

ngắ

t.

Mộ

t ví

dụ

đi nể

hình

về

ngắ

t

là

vi cệ

nh pậ

dử

liệu

b ngằ

tay

dùng

bàn

phím.

Hãy

kh oả

sát

mộ

t

ứng

d ngụ

về

lò

vi

sóng:

Chưngơ

trình

chính

đi uề

khi nể

ph nầ

t

ử

t

oạ

năng

lưngợ

vi

sóng

để

n uấ

ă

n,

nhưng

t

rong

khi

đang

n uấ

hệ

th

ống

c nầ

phả

I

đáp

ứng

việc

nh pậ

b ngằ

tay

trên

c aử

lò

ví

dụ

t

ăng

ho cặ

giãm

th

ờ

I

gian

nấ

u.

Khi

ngườ

I

xử

d ngụ

th

ả

nút

nhấ

n,

mộ

t

ngắ

t

đ cượ

t

oạ

ra

(có

th

ể

là

mộ

t tín

hi uệ

chuy nể

t

ừ

mức

cao

xu ngố

mức

th

p)ấ

và

chương

trình

chính

bị

dừng

lạ

I,

chương

trình

ISR

hoạ

t

đ ngộ

đ cọ

các

mả

c aủ

bàn

phím

và

thay

đổ

I

quá

trình

n uấ

t

ưngơ

ứng

sau

đó

ch mấ

dứ

t

b ngằ

cách

chuy nể

đi uề

khi nể

về

cho

chưngơ

trình

chính,

chương

trình

chính

lạ

I ti

pế

t

ục

t

ừ

n iơ

bị

ngắ

t.

Mộ

t

đi mể

quan

tr

ngọ

trong

ví

dụ

này

là

vi cệ

nh pậ

b ngằ

tay

x yả

ra

mộ

t

cách

không

đ ngồ

bộ

có

nghĩa

là

không

biế

t tr

ưcớ

ho cặ

không

đ cượ

đi uề

khi nể

b ngằ

ph nầ

m mề

đang

ch yạ

trong

hệ

th

ng.ố

Đó

chính

là

đ cặ

đi mễ

c aủ

ngắ

t

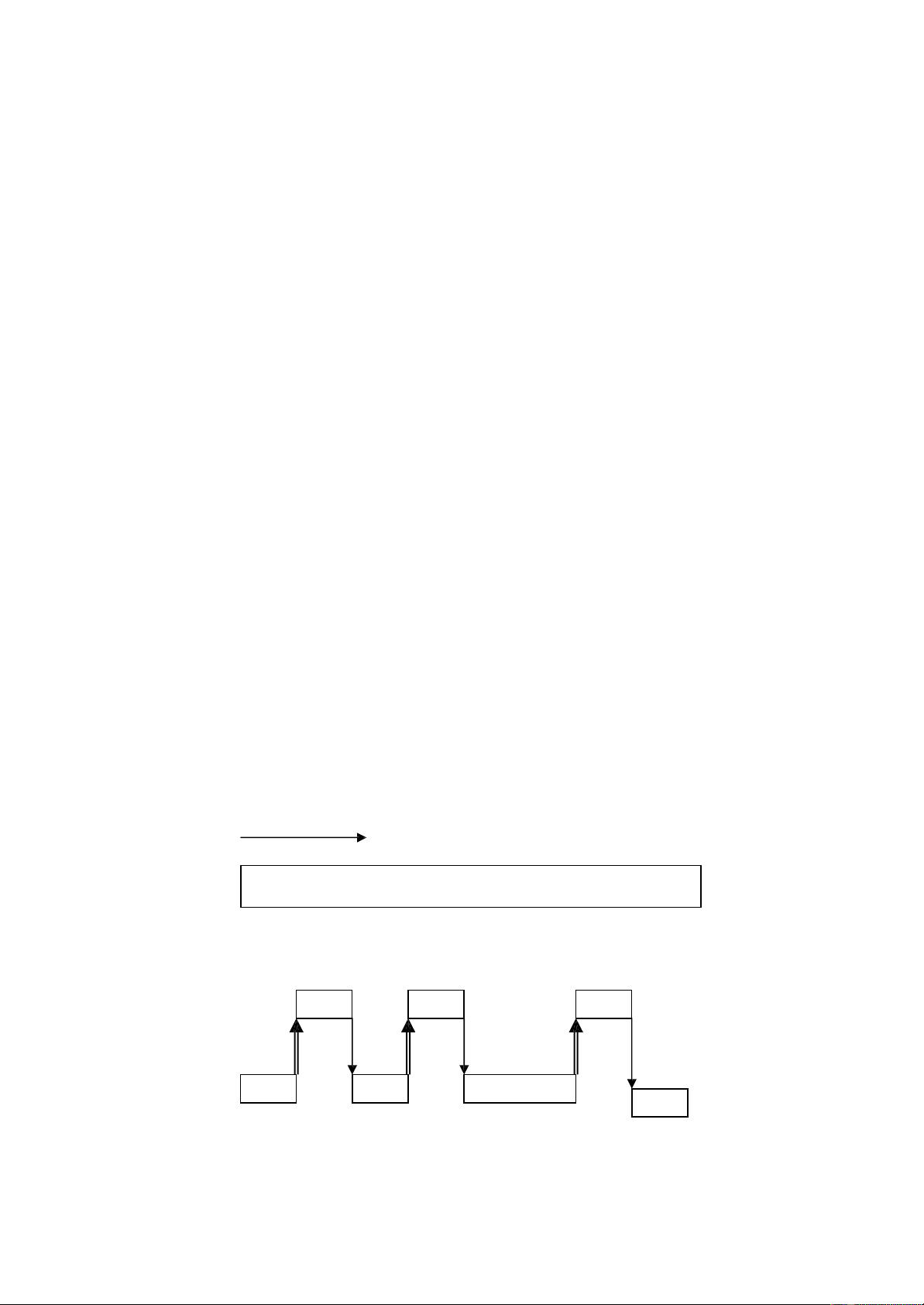

Thời gian

Chương trình chính

a) Thực hiện chương trình không có ngắt

ISR ISR ISR

main main main main

b) Thực hiện chương trình với ngắt

Hình 6.1 Thực hiên chương trình

2

2.

T

Ổ

CH CỨ

NGẮ

T

CỦA

8051

8051

có

năm

ngu nồ

tín

hi uệ

ngắ

t:

2

ngắ

t

ngoà

i,

2

ngắ

t

đ nhị

th

iờ

và

1

ngắ

t

c ngổ

n iố

ti

ế

p.

8052

có

thêm

ngắ

t th

ứ

sáu

của

timer

th

ứ

ba.

Tr ngạ

thái

m cặ

định

c aủ

các

ngắ

t

là

không

hoạ

t

đ ngộ

sau

khi

reset

hệ

th

ngố

và

chuy nể

sang

hoạ

t

đ ngộ

t

ừng

ngắ

t

riêng

rẻ

b ngằ

ph nầ

m m.ề

Trong

tr

ưngờ

h pợ

có

hai

ho cặ

nhi uề

ngắ

t

xuấ

t

hi nệ

đ ngồ

th

ời

ho cặ

mộ

t

ngắ

t

x yả

ra

trong

khi

mộ

t

ngắ

t

khác

đang

đ cượ

ph cụ

vụ

.

Có

hai

sơ

đồ

s pắ

x pế

ưu

tiên

các

ngắ

t

đó

là:

Chu iỗ

pooling

và

ưu

t

iên

hai

cấ

p, t

hứ

t

ự

theo

chu iỗ

pooling

thì

cố

định

nhưng

sơ

đồ

ưu

tiên

hai

c pấ

thì

l pậ

trình

đượ

c.

Sau

đây

là

phưngơ

pháp

cho

phép

và

không

cho

phép

sự

hoạ

t

đ ngộ

c aủ

các

ngắ

t.

Cho phép và không cho phép các ng tắ

M iỗ

mộ

t tín

hi uệ

ngắ

t

đ cượ

cho

phép

ho cặ

không

cho

phép

b iở

đ aị

chỉ

bít

trong thanh

ghi

chức

năng

đ cặ

biệ

t IE (I

nterrupt

enable)

t

iạ

đ aị

chỉ

0A8H,

có

mộ

t bít

cho

phép toàn

cụ

c, bít

này

khi

bị

xóa

sẻ

ngăn

t

ấ

t

cả

các

ngắ

t.

(b ngả

6.

1).

Để

cho

phép

mộ

t

ngắ

t

c nầ

ph iả

set

hai

bít:

Mộ

t bít

cho

phép

riêng

và

b

ít

cho

phép

toàn

cụ

c. V

D

Ngắ

t

timer

1

đ cượ

cho

phép

như

sau:

SETB

ET1

SETB EA

Ho cặ

MOV IE,#10001000B

M cặ

dù

hai

cách

trên

có

cùng

kế

t

quả

sau

khi

reset

hệ

th

ngố

nhưng

kế

t

quả

sẻ

khác

nhau

n uế

IE

được

ghi

ở

giữa

chưngơ

trình

trong

khi

đang

chạ

y.

Cách

th

ứ

nhấ

t

không

nhả

hưngỡ

đ nế

5

bít

còn

lại

trong

thanh

ghi

IE

còn

cách

th

ứ

hai

sẻ

xóa

các

bít

còn

lại

khác.

T

ố

t

nhấ

t

nên

dùng

cách

th

ứ

hai

t

iạ

vị

trí

bắ

t

đ uầ

chưngơ

trình

(nghĩa

là

khi

bắ

t

đ uầ

mở

máy

ho cặ

reset

hệ

th

nốg)

nên

dùng

l nhệ

SETB

và

CLR

trong

khi

chưngơ

trình

đang

ch yạ

để

tránh

nhả

hưngỡ

các

bít

khác

trong

thanh

ghi

IE.

M c u tiênứ ư

M iỗ

ngắ

t

đ cượ

l pậ

trình

ở

mộ

t

trong

hai

mức

ưu

tiên

bằng

thanh

ghi

IP

(Interrupt

priority)

t

iạ

đ aị

chỉ

oB8H

(b ngả

6.2)

Thanh

ghi

IP t

ự

đ ngộ

xóa

sau

khi

reset

hệ

th

ngố

để

đặ

t

các

ngắ

t

ở

mức

ưu

tiên

th

pấ

B

NGẢ

6.1

Thanh

ghi

IE

BÍT Ký

hi

uệĐ aị

chỉ

bít Mô

tả

(1=cho

phép,

0=không

cho

phép)

IE.7

IE.6

IE.5

IE.4

IE.3

IE.2

IE.1

IE.0

EA

-

ET2

ES

ET1

EX

1

ET0

EX

0

AFH

AEH

ADH

ACH

ABH

AAH

A9H

A8H

Cho

phép

toàn

c cụ

Không

dùng

Cho

phép

ngắ

t

timer

2

(8052)

Cho

phép

ngắ

t

c ngổ

n iố

ti

pế

Cho

phép

ngắ

t

timer

1

Cho

phép

ngắ

t

1

ngoài

Cho

phép

ngắ

t

timer

0

Cho

phép

ngắ

t

0

ngoài

B

NGẢ

6.2

Thanh

ghi

IP

BÍT Ký

hi

uệĐ aị

chỉ

bít Mô

tả

(1=mức

cao,

0=mức

th p)ấ

IP.7

IP.6

IP.5

IP.4

IP.3

IP.2

IP.1

IP.0

-

-

PT2

PS

PT1

PX

1

PT0

PX

0

-

-

0BDH

0BCH

0BBH

0BAH

0B9H

0B8H

Không

dùng

Không

dùng

uƯ

tiên

ngắ

t

timer

2

(8052)

uƯ

tiên

ngắ

t

c ngổ

n iố

ti

ếp

uƯ

tiên

ngắ

t

timer

1

uƯ

tiên

ngắ

t

1

ngoài

uƯ

tiên

ngắ

t

timer

0

uƯ

tiên

ngắ

t

0

ngoài

Khái

ni mệ

“ưu

tiên”

cho

phép

mộ

t IS

R

bị

dừng

b iở

mộ

t

ngắ

t

khác

n uế

ngắ

t

m iớ

xuấ

t

hi nệ

này

có

mức

ưu

tiên

cao

h nơ

ngắ

t

đang

được

ph cụ

vụ

,

đi uề

này

phù

h pợ

v iớ

8051

vì

chỉ

có

hai

mức

ưu

tiên,

n uế

mộ

t ISR

ưu

tiên

th

pấ

đang

chạy

nhưng

l iạ

x yả

ra

mộ

t

ngắ

t

ưu tiên

cao

thì IS

R

sẻ

bị

dừng.

Mộ

t ISR

ưu

tiên

không

th

ể

bị

dừng

.

Chưngơ

trình

chính

hoạ

t

đ ngộ

ở

mức

ưu

tiên

cơ

sở

và

không

liên

hệ

v iớ

mộ

t

ngắ

t

bấ

t

kỳ

nào

nên

luôn

bị

dừng

khi

x yả

ra

ngắ

t.

N uế

hai

ngắ

t

có

mức

ưu

tiên

khác

nhau

cùng

x yả

ra

thì

ngắ

t

có

mức

ưu

tiên

cao

sẻ

đ cượ

phục

vụ

tr

ướ

c.

Chu iỗ pooling

N uế

đ ngồ

th

iờ

xuấ

t

hi nệ

hai

ngắ

t

có

cùng

mức

ưu

tiên

thì

ngắ

t

đ cượ

ph cụ

vụ

tr

ưcớ

đ cượ

xác

định

theo

th

ứ

t

ự

chu iỗ

pooling:

Ngắ

t

0

ngoài,

ngắ

t

timer

0,

ngắ

t

1

ngoài,

ngắ

t

timer

1,

ngắ

t

c ngổ

n iố

ti

ế

p,

ngắ

t

timer

2.

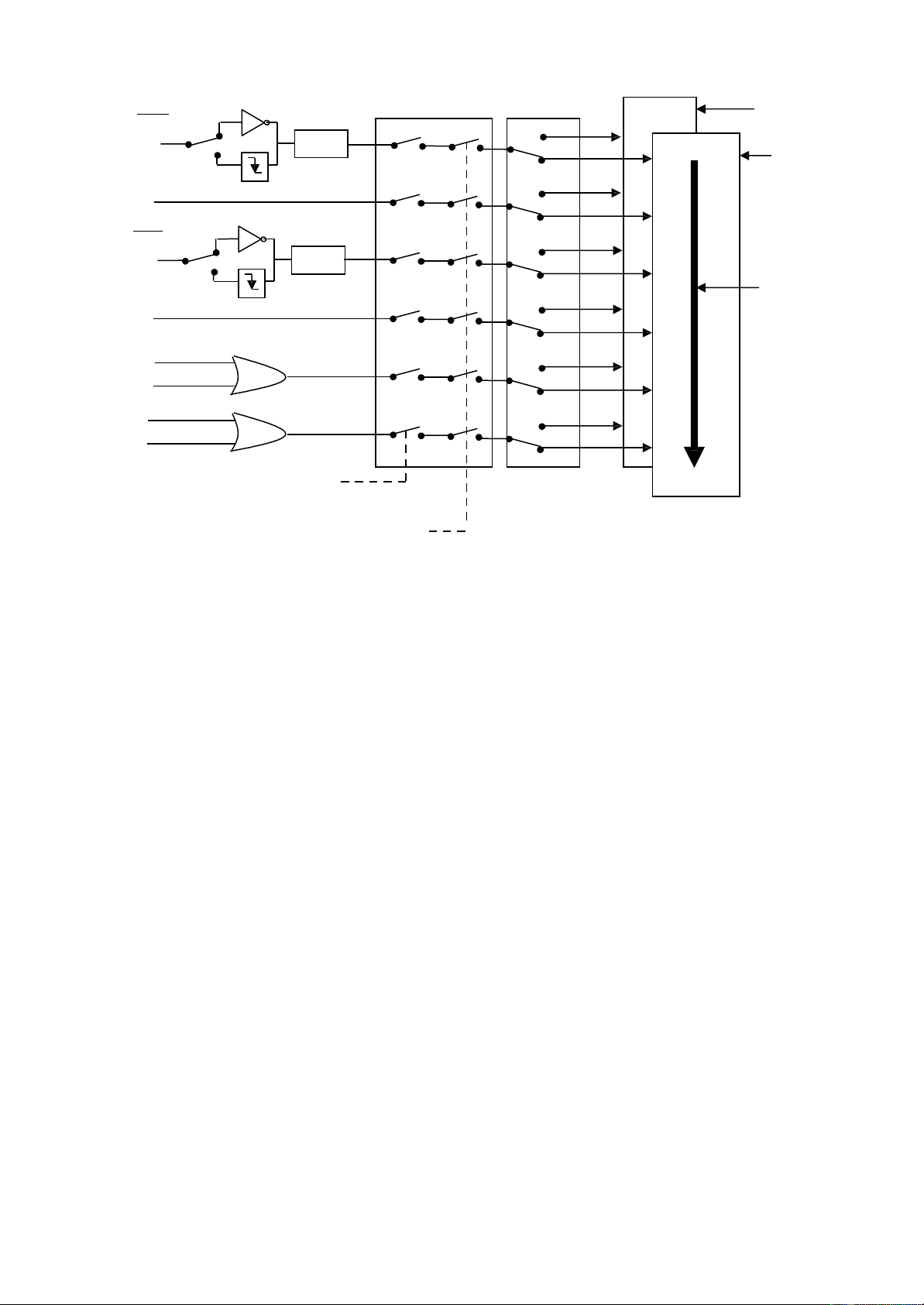

Hình

6.2

trình

bày

năm

ngu nồ

tín

hi uệ

ngắ

t

cùng

cơ

chế

cho

phép

toàn

c cụ

và

riêng

rẻ

,

chu iỗ

pooling

và

các

mức

ưu

tiên,

tr

ngạ

thái

c aủ

t

ấ

t

cả

các

ngu nồ

tín

hi uệ

ngắ

t

có

th

ể

thông

qua

các

bít

cờ

trong

thanh

ghi

chức

năng

đ cặ

biệ

t.

Dỉ

nhiên,

n uế

mộ

t

ngắ

t

nào

đó

không

đ cượ

cho

phép

thì

ngắ

t t

ưngơ

ứng

không

đ cượ

t

oạ

ra

nhưng

ph nầ

mềm

v nẩ

có

th

ể

ki mể

tra

cờ

ngắ

t.

Các

ví

dụ

về

timer

và

cổng

n iố

ti

pế

trong

hai

bài

tr

ưcớ

đã

sử

d ngụ

các

cờ

ngắ

t

mà

th

ực

t

ế

không

dùng

các

ngắ

t.

Mộ

t

ngắ

t

c ngổ

n iố

ti

pế

là

kế

t

quả

t

ừ

phép

OR

c aủ

ngắ

t th

u

(RI)

v iớ

ngắ

t

phát

(TI

)

.

T

ưngơ

t

ự

,

ngắ

t

timer

2

đ cượ

t

oạ

ra

b iở

cờ

tràn

TF2

ho cặ

v iớ

cờ

nh pậ

bên

ngoài

EX

F2

.

Khả

năng

t

oạ

ngắ

t

c aủ

các

bít

cờ

đ cượ

tóm

t

ắ

t

trong

b ngả

6.

3

3.

X

Ử

LÝ

NGẮ

T

Khi

mộ

t

ngắ

t

xuấ

t

hi nệ

đ cượ

CPU

nh nậ

ra,

chưngơ

trình

chính

sẻ

dừng

l iạ

và

kế

ti

pế

là

các

t

hao

tác

như

sau:

•Thực

hi nệ

hoàn

t

ấ

t

l nhệ

hi nệ

hành

•Lưu

n iộ

dung

thanh

ghi

PC

vào

ngăn

x pế

•Lưu

tr

ngạ

th

ái

ngắ

t

hi nệ

hành

•Các

ngắ

t

đ cượ

ch nặ

l iạ

t

iạ

mức

ngắ

t

•N pạ

đ aị

chỉ

vec

t

ơ

c aủ

ISR

vào

PC

•Thực

hi nệ

IS

R

Chưngơ

trình

ISR

hoạ

t

đ ngộ

và

th

ực

hi nệ

các

t

hao

tác

t

ương

ứng

v iớ

ngắ

t.

Sau

đ

ó,

kế

t

thúc

khi

g pặ

l nhệ

R

ETI

(return

from

interrupt),

l nhệ

này

l yấ

l iạ

giá

tr

ị

c aủ

PC

t

ừ

ngăn

x pế

và

ph cụ

h iồ

tr

ngạ

th

ái

ngắ

t

củ

,

chưngơ

trình

ti

pế

t

cụ

chạy

t

ừ

n iơ

t

mạ

dừng.

B

NGẢ

6.3

Các

bít

cờ

ngắ

t

Ng tắCờThanh

ghi

SFR

và

vị

trí

bít

0

ngoài

1

ngoài

timer

1

timer

0

c ngổ

n iố

ti

ếp

c ngổ

n iố

ti

ếp

timer

2

timer

2

IE0

IE1

TF1

TF0

Ti

Ri

TF2

EX

F2

TCON.1

TCON.3

TCON.7

TCON.5

SCON.1

SCON.0

T2CON.7

(8052)

T2CON.6

(8052)

INT0

TF0

IE0

u tƯiên cao

u tiƯên thấp

INT1

IE1

TF1 Chuỗi

pooling

Ri

Ti

TF2

EXF2

Cho phép riêng

Cho phép toàn cục

Hình 6.2 Cấu trúc ngắt 8051

Các vec tơ ng tắ

Khi

mộ

t

ngắ

t

đ cượ

ch pấ

nhậ

n,

giá

tr

ị

n pạ

vào

bộ

đ mế

chưngơ

trình

PC

đ cượ

g iọ

là

véc

t

ơ

ngắ

t.

Đây

là

đ aị

chỉ

bắ

t

đ uầ

c aủ

ISR

đ iố

v iớ

ngắ

t t

ưngơ

ứng.

Các

véc

t

ơ

ngắ

t

đ cượ

cho

trong

bẳng

6.4.

Véc

t

ơ

reset

hệ

th

ngố

(RST

t

iạ

đ aị

chỉ

0000H)

cũng

đ cượ

cho

trong

b ngả

nên

nó

cũng

gi ngố

như

mộ

t

ngắ

t,

nó

dừng

chưngơ

trìn

h

chính

và

n pạ

vào

PC

mộ

t

giá

tr

ị

mớ

i.

Khi

tr

ỏ

đ nế

mộ

t

ngắ

t,

cờ

gây

ra

ngắ

t

sẻ

bị

xóa

t

ự

đ ngộ

bị

xóa

b iở

ph nầ

cứng

ngo iạ

tr

ừ

Ri

và

Ti

đ iố

v iớ

ngắ

t

c ngổ

nối

ti

pế

và

TF2, EX

F2

đ iố

v iớ

ngắ

t

timer

2.

Do

có

hai

nguyên

nhân

t

oạ

ngắ

t

cho

các

ngắ

t

này

nên

th

ậ

t

là

không

t

hực

t

ế

n uế

CPU

xóa

cờ

ngắ

t.

Các

bít

này

ph iả

đ cượ

ki mể

tra

trong

ISR

để

xác

đ nhị

nguyên

nhân

t

oạ

ngắ

t

và

sau

đó

cờ

ngắ

t

đ cượ

xóa

b ngằ

ph nầ

m m,ề

th

ưngờ

có

mộ

t

sự

rẻ

nhánh

đ nế

các

t

hao

tác

t

ương

ứng

phụ

thu cộ

vào

ngu nồ

t

oạ

ra

ngắ

t.

Vì

các

véc

t

ơ

ngắ

t

được

đặ

t

phía

dưiớ

đáy

c aủ

bộ

nhớ

chưngơ

trình

nên

l nhệ

đ u tiênầ

c aủ

chưngơ

trình

chính

th

ưngờ

là

l nhệ

nh yả

qua

vùng

này

VD

l nhệ

LJMP

0030H.

4.

THIẾ

T

KẾ

CHƯƠNG

TRÌNH

DÙNG

NGẮ

T

Trong

các

bài

tr

ưcớ

đây

đã

không

dùng

đ nế

ngắ

t

mà

dùng

nhi uề

các

vòng

l pặ

để

ki mể

tra

cờ

tràn

c aủ

timer

TF0,

TF1

ho cặ

TF2

ho cặ

các

cờ

thu

phát

của

c ngổ

n iố

ti

pế

Ti

ho cặ

Ri,

v nấ

đề

c aủ

phưngơ

pháp

này

là

th

iờ

gian

hoạ

t

đ ngộ

c aủ

CPU

hoàn

toàn

được

dùng

vào

vi cệ

chờ

các

cờ

này

được

set,

đi uề

này

hoàn

toàn

không

thích

h pợ

v iớ

các

ứng

d ngụ

hưngớ

đi uề

khi nể

mà

trong

đó

yêu

c uầ

vi

đi uề

khi nể

ph iả

đ ngồ

th

iờ

t

ưngơ

tá

c

v iớ

nhi uề

thiế

t

bị

vào

ra.

Mộ

t ví

dụ

trong

ph nầ

này

sẻ

minh

h aọ

các

phưngơ

pháp

th

ực

t

ế

viế

t

ph nầ

m mề

cho các

ứng

dụng

hưngớ

đi uề

khiể

n, t

hành

ph nầ

chính

là

các

ngắ

t.

M cặ

dù

các

v

í

dụ

này

![Thu truyền hình cáp trên máy vi tính [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130322/bibocumi35/135x160/1390540_056.jpg)