ME3081: Mechatronic System Design

2

Lecturer: PhD. Dang Thai Viet

Mechatronic Department, School of Mechanical Engineering, HUST

Viet.dangthai@hust.edu.vn

Chương 5. Chất lượng hệ thống Cơ điện tử

3

Mục 2. Sai số xác lập

Mục 3. Đáp ứng quá độ

Mục 4. Quan hệ tần số với chất lượng hệ thống trong miền thời gian

Mục 1. Chỉ tiêu chất lượng hệ thống

ME3081: Mechatronic System Design

4

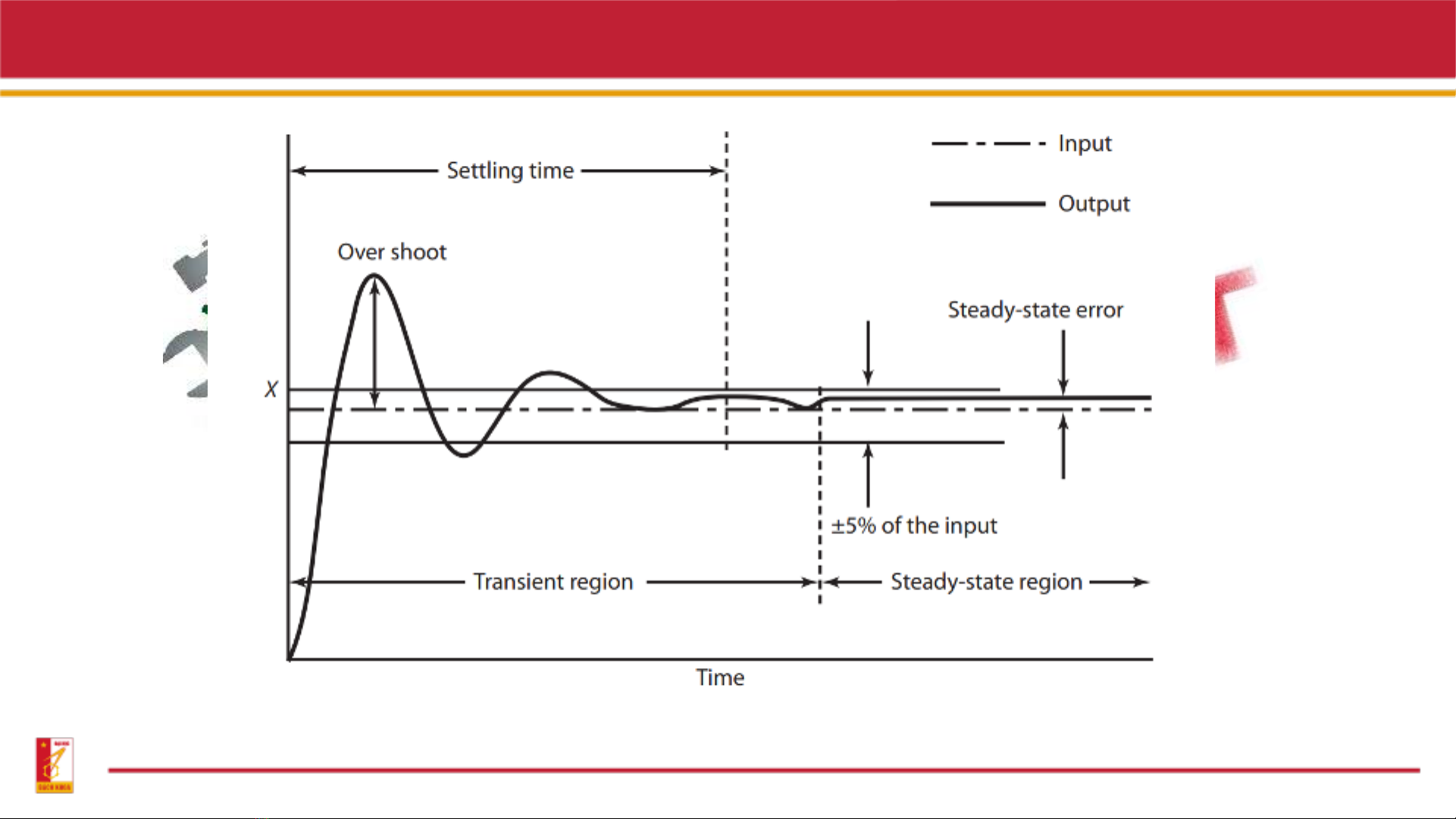

•Ổn định là điều kiện cần của một hệ thống.Một hệ thống ổn định chưa đủ chính xác hay quá trình

quá độ dài hạn.

•Cần khảo sát quá trình điều khiển hệ thống, dùng các tín hiệu thường gặp (phổ biến)hoặc dạng tác

động hiếm gặp (đột biến)

•Các tín hiệu phổ biến dạng bậc thang đơn vị, dạng hàm tăng dần đều hay sóng điều hòa.

❑Chất lượng hệ thống

5.1. Chỉ tiêu chất lượng hệ thống (1)

5

Hình 5.1. Quá trình quá độ và xác lập của hệ thống theo thời gian thực

5.1. Chỉ tiêu chất lượng hệ thống (2)

![Thiết kế cung cấp điện cho Nhà máy cơ khí Duyên Hải: Bài tập lớn [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260417/choang102426@st.vimaru.edu.vn/135x160/52181776391564.jpg)