HARDWARE C AỦ

SOCCER ROBOT

2.1 Gi i thi u chung v hardware c a soccer robot:ớ ệ ề ủ

Soccer robot bao g m CPU MR188 board, board đi u khi n đ ng c , RF(vô tuy n)ồ ề ể ộ ơ ế

module.Đ tăng s ho t đ ng c a robot, b đi u khi n CPLD đ c s d ng đ đi uể ự ạ ộ ủ ộ ề ể ượ ử ụ ể ề

khi n đ r ng xung PWM đ ng c và các tín hi u encoder.CPLD là ph ng ti n tr giúpể ộ ộ ộ ơ ệ ươ ệ ợ

cho vi c l p trình đi u khi n.ệ ậ ề ể

Hardware c a robot c th nh sau:ủ ụ ể ư

•CPU:Kích th c 72mmx46mm(MR188A1 Board)ướ

• RF và Motor Control Board:71.5mmx72.5mm

• DC motor:

-H p s : 7.5:1ộ ố

-T c đ t i đa:1.5m/s.ố ộ ố

•Encoder: 512 pulse/vòng

• Pin: 7.2V,450mAh

• RF Module: BiM-418 ho c BiM-433ặ

• Driver đ ng c DC:L298ộ ơ

• DC motor controller: CY37128(CPLD)

2.2 RF Module:

2.2.1 RF Module là gì?

RF (Radio Frequency) module là thi t b s d ng đ truy n thông sóng vô tuy n.ế ị ử ụ ề ề ế

Trong tr ng h p này t n s sóng vô tuy n đ c p đ n sóng đi n thông d ng và không chườ ợ ầ ố ế ề ậ ế ệ ụ ỉ

là t n s vô tuy n phát thanh. RF module có th đ c phân lo i theo t n s , ph ng phápầ ố ế ể ượ ạ ầ ố ươ

đi u bi n (s bi n đ i c a tín hi u d ng s sang d ng t ng t , th ng dùng trong truy nề ế ự ế ổ ủ ệ ạ ố ạ ươ ự ườ ề

tín hi u qua các h th ng vi n thông), d li u, c ng đ ngõ ra…ệ ệ ố ễ ữ ệ ườ ộ

2.2.2 Charisma RF Board:

M ch giao ti p vô tuy n Charisma chuy n đ i d li u n i ti p RS232 sang d li uạ ế ế ể ổ ữ ệ ố ế ữ ệ

RF và ng c l i. Charisma Board có th d dàng k t n i v i các thi t b s d ng c ngượ ạ ể ễ ế ố ớ ế ị ử ụ ổ

RS232. Charisma đ c thi t k s d ng RadioMetrix BiM,TX2 hay RX2ượ ế ế ử ụ

modules. PC và PC cũng có th giao ti p đ c v i nhau n u c 2 PC đ u k t n i v iể ế ượ ớ ế ả ề ế ố ớ

Charisma board.

2.3 Radiometrix BiM-UHF:

2.3.1 Đ nh nghĩa và ng d ng Radiometrix:ị ứ ụ

BiM-418-F và BiM-433F là nh ng module vô tuy n UHF thu nh có kh năng truy nữ ế ỏ ả ề

d li u đ n công v i t c đ lên đ n 40Kbit/s và kho ng cách truy n lên đ nữ ệ ơ ớ ố ộ ế ả ề ế

30m(trong nhà) và 120m(ngoài tr i).ờ

T n s T c đ Kho ng cách Ngu n Antenầ ố ố ộ ả ồ

BiM-418-F 418MHz 40K bps 30-120m 4.5V-5.5V 16.5cm

BiM-433-F 433.92MHz 40H bps 30-120m 4.5V-5.5V 16.5cm

Module này tích h p b phát UHF FM năng l ng th p, b thu đ i t n s phù h pợ ộ ượ ấ ộ ổ ầ ố ợ

v i ph c h i d li u và nh ng m ch chuy n đ i TX/RX đ cung c p m t gi i pháp kinhớ ụ ồ ữ ệ ữ ạ ể ổ ể ấ ộ ả

t trong th c hi n vi c liên k t d li u b ng sóng vô tuy n t m ng n theoế ự ệ ệ ế ữ ệ ằ ế ầ ắ

2 chi u. T c đ d li u cao (40kbit/s) và s chuy n đ i TX/RX nhanh(<1ms) làm cho bề ố ộ ữ ệ ự ể ổ ộ

phát BiM lý t ng cho vi c truy n nguyên v n thông tin c a nh ng liên k t one-to-one vàưở ệ ề ẹ ủ ữ ế

m ng.ạ

Nh ng ng d ng th c t c a module:ữ ứ ụ ự ế ủ

•Nh ng m ng máy tính có t c đ trung bình.ữ ạ ố ộ

• Nh ng báo đ ng v an ninh/c u h a.ữ ộ ề ứ ỏ

• Vi c đi u khi n / hi n th trong các tòa nhà.vvệ ề ể ể ị

2.3.2 Mô t các chân :ả

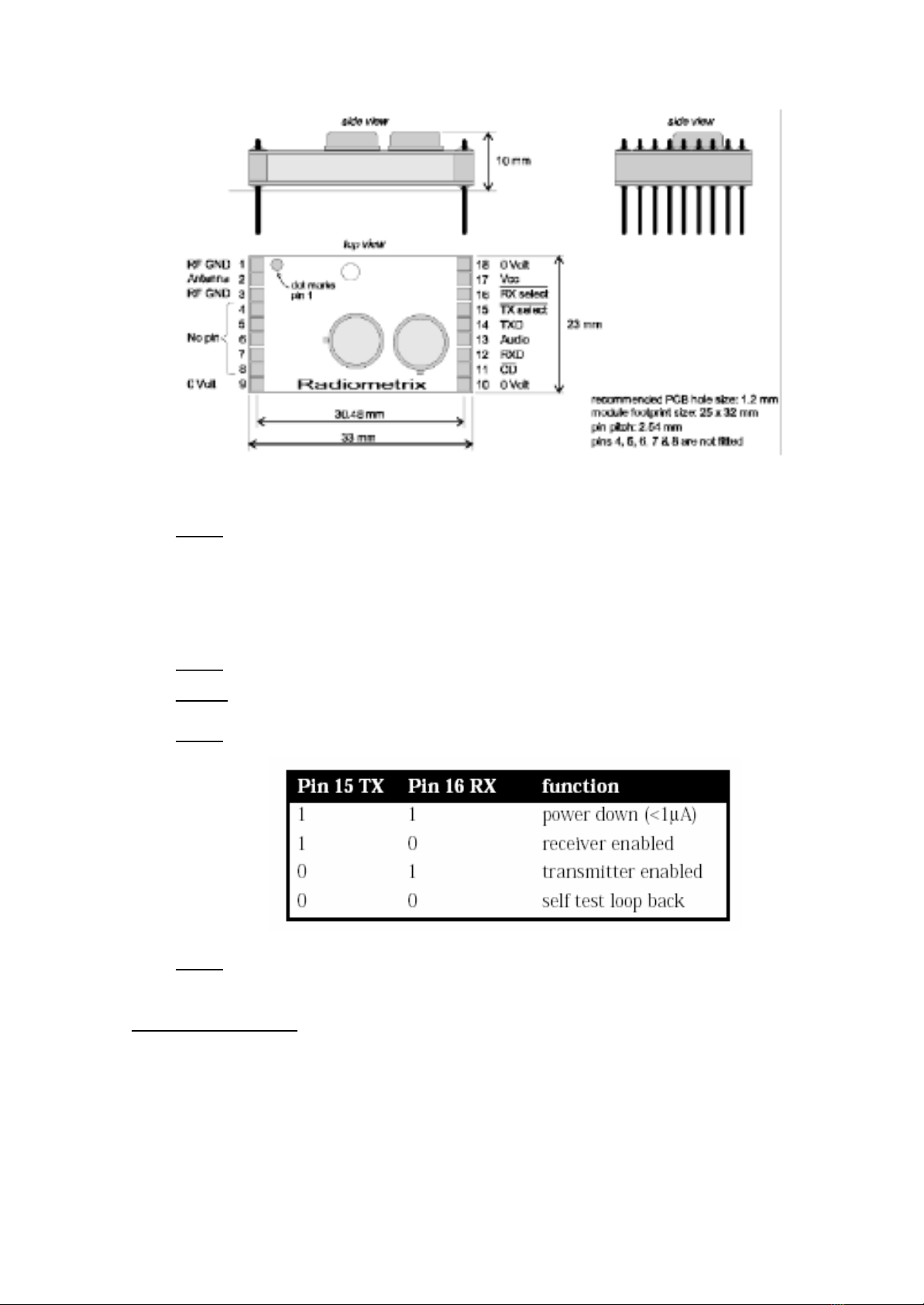

Hình 2.1: Mô t các chân c a Radiometrix.ả ủ

Pin13:Đây là ngõ ra c a đi u ch FM. Nó có DC bias hi n hành kho ngủ ề ế ệ ả x p xấ ỉ

1.5V và có th đ c s d ng đ lái nh ng b gi i mã d li u t ng t nh là nh ng bể ượ ử ụ ể ữ ộ ả ữ ệ ươ ự ư ữ ộ

gi i mã modem. Tr kháng ngõ ra là 10kOhm. Ngõ ra ch là d li u th c cho BiM-418 vàả ở ỉ ữ ệ ự

đ o ng c l i v i BiM-433.ả ượ ạ ớ

Pin14 (TXD): Ngõ vào này luôn <0.5V khi TX không đ c ch n.ượ ọ

Pin 15 (TX select):S l a ch n truy n/nh n v i đi n tr trong 10kOhm.ự ự ọ ề ậ ớ ệ ở

Pin16 (RX select): Có th đ c lái b ng c c thu h ho c là CMOS logic.ể ượ ằ ự ở ặ

Pin17: VCC: có th s d ng các ngu n áp t 4.5-5.5 V. Đ g n sóng t i đa làể ử ụ ồ ừ ộ ợ ố

50mV đ nh-đ nh.ỉ ỉ

2.4 Charisma board:

2.4.1 S đ b trí:ơồố

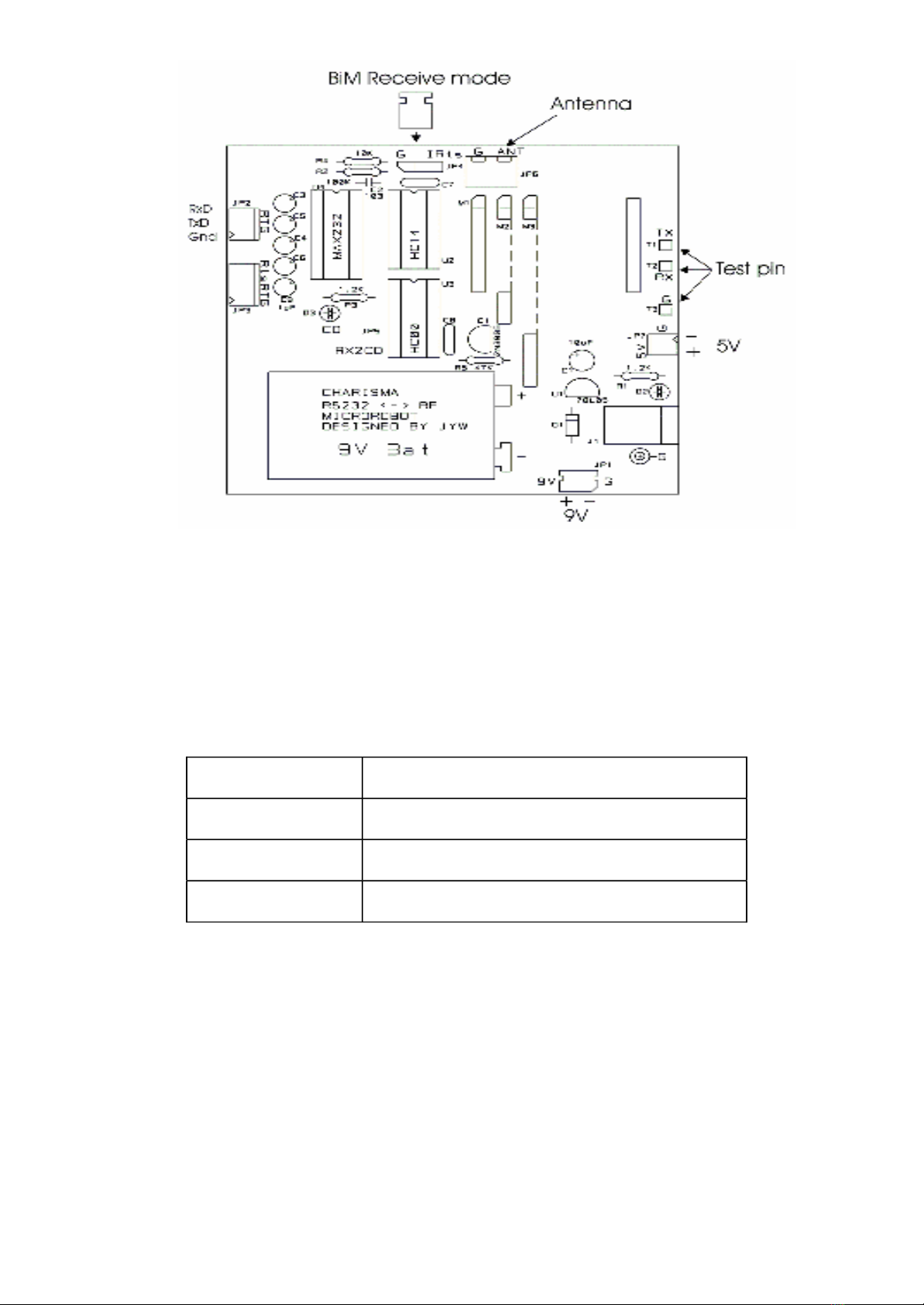

Hình 2.2: S đ b trí c a m ch giao ti p RF.ơ ồ ố ủ ạ ế

2.4.2 Cài đ t module:ặ

Module RF là các module giao ti p 2 chi u.Đ ch n ch đ truy n và nh n có thế ề ể ọ ế ộ ề ậ ể

s d ng ph ng pháp ph n m m và ph n c ng.Ph ng pháp ph n m m s d ng chânử ụ ươ ầ ề ầ ứ ươ ầ ề ử ụ

RTS c a c ng RS232.Ph ng pháp ph n c ng s d ng kh i jumper nh sau:ủ ổ ươ ầ ứ ử ụ ố ư

Cài đ t jumper Ch đặ ế ộ

1,2 Nh nậ

2,3 Ph ng pháp ph n m m (truy n và nh n)ươ ầ ề ề ậ

Empty Truy n, phátề

![Robot song song P2: [Thêm từ mô tả hấp dẫn, ví dụ: Hướng dẫn chi tiết, Cách chế tạo hiệu quả]](https://cdn.tailieu.vn/images/document/thumbnail/2010/20100323/tanlang/135x160/robot_song_song_2_9234.jpg)

![Giáo trình Tự động hóa quá trình sản xuất: Phần 2 [Đầy đủ/Chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/6191777378796.jpg)