Xung & Hoi1

1.Giớithiệu

2.Sơđồ khốivàchân

3.Tổchứcbộnhớ

4.

4. C

Cá

ác

cthanh

thanh ghi

ghi ch

chứ

ức

cnăng

năng đ

đặ

ặc

cbi

biệ

ệt

t(SFR)

(SFR)

5.Dao độngvàhoạtđộngreset

6.Tậplệnh

7.Cácmode định địachỉ

8.LậptrìnhIO

9.Tạotrễ

10.LậptrìnhTimer/Counter

11.Lậptrìnhgiaotiếpnốitiếp

12.Lậptrìnhngắt

13.Lậptrìnhhợpngữ

Xung & Hoi2

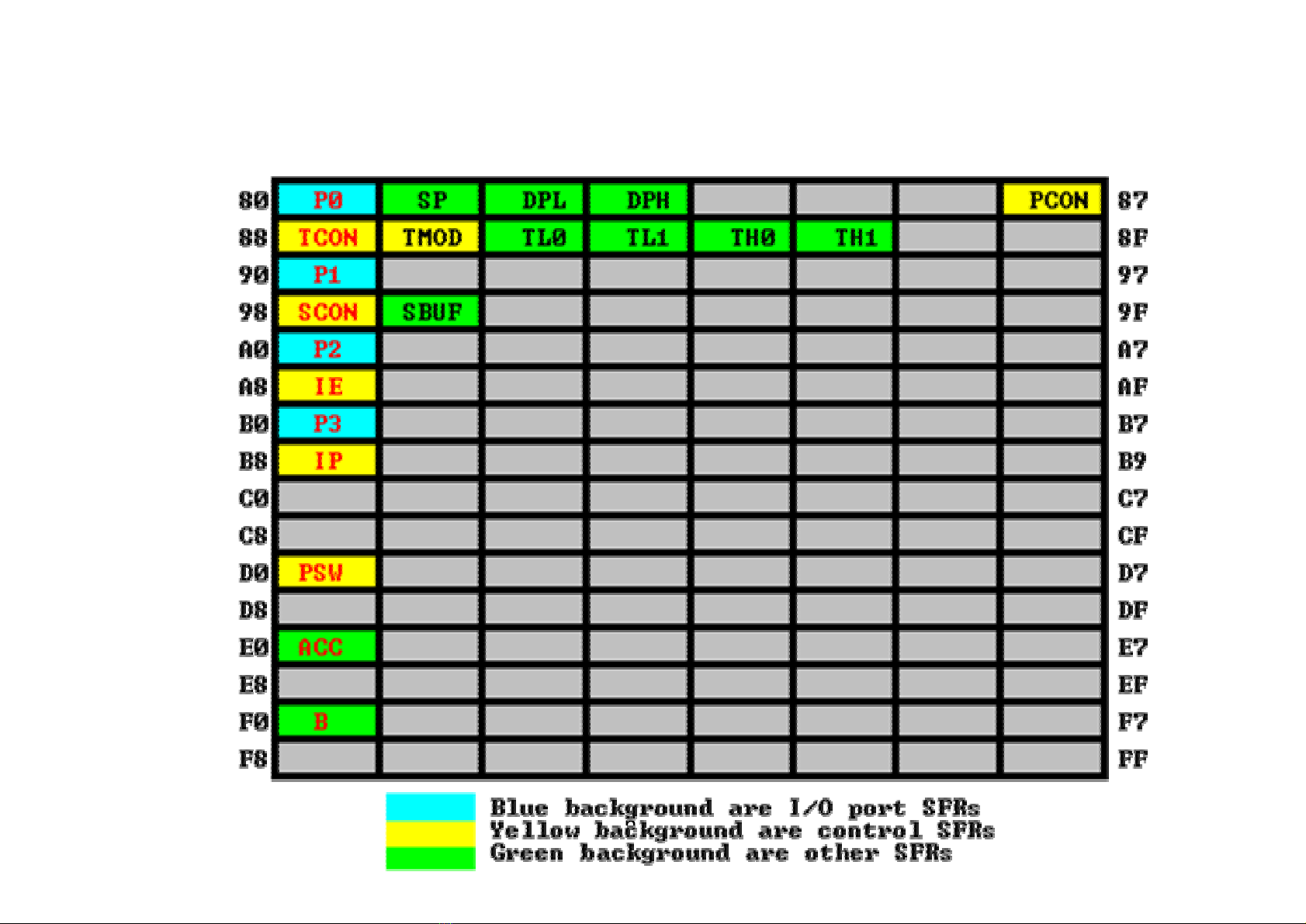

XêmthêmHình2.6 trang26

SFRs

Xung & Hoi3

CPU registers:

-ACC: Accumulator.

-B: B register.

-PSW: Program Status Word.

-SP: Stack Pointer.

-DPTR: Data Pointer (DPH, DPL).

Interrupt control:

-IE: Interrupt Enable.

-IP: Interrupt Priority.

I/O Ports:

-P0: Port 0.

-P1: Port 1.

-P2: Port 2.

-P3: Port 3.

Xung & Hoi4

TImers:

-TMOD: Timer mode.

-TCON: Timer control.

-TH0: Timer 0 high byte.

-TL0: Timer 0 low byte.

-TH1: Timer 1 high byte.

-TL1: Timer 1 low byte.

Serial I/O:

-SCON: Serial port control.

-SBUF: Serial data registers.

Other:

-PCON: Power control & misc.

Xung & Hoi5

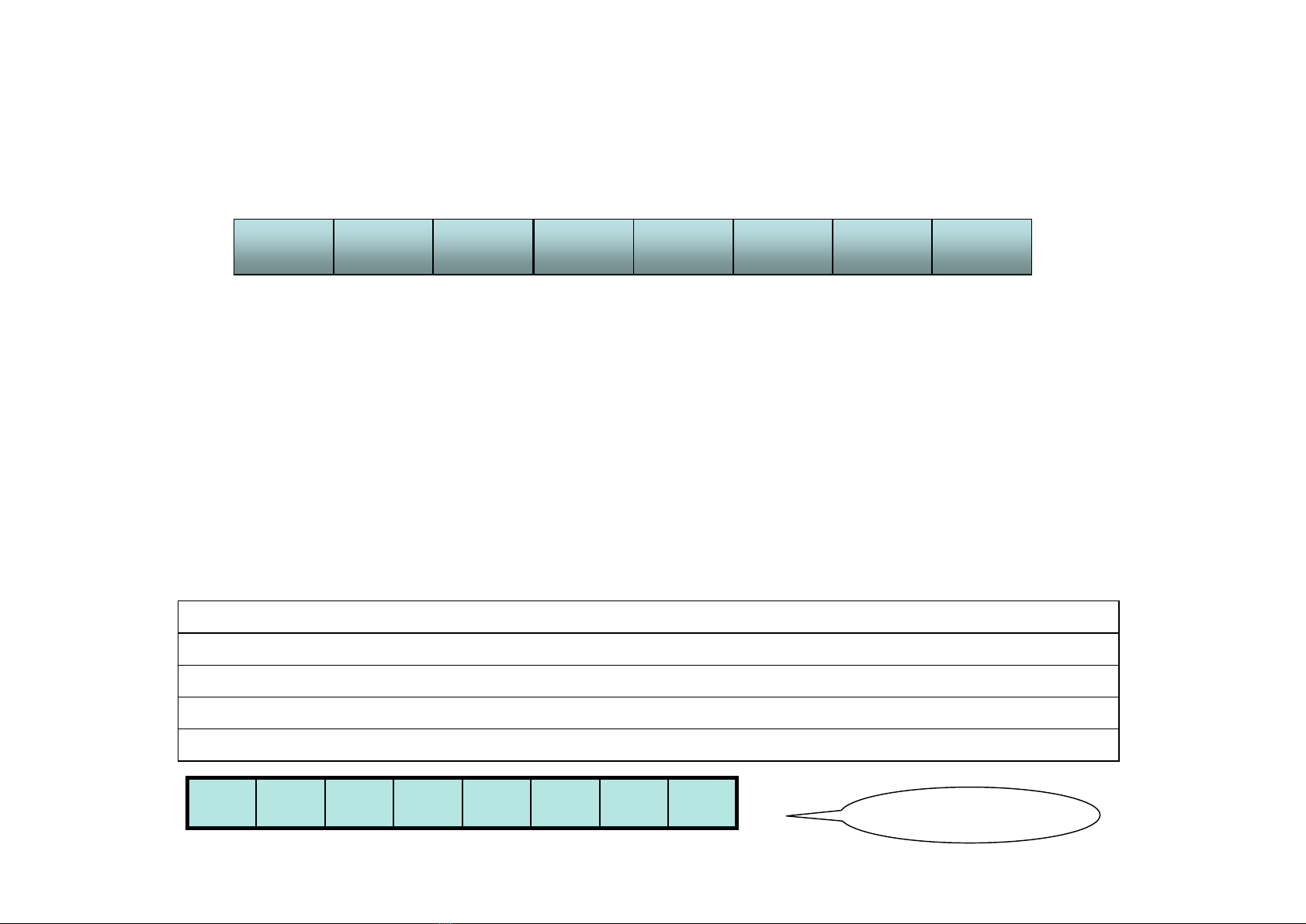

4-1. ThanhghiPSW

•ThanhghiPSW (bit addressable)

CAC F0 RS1 OVRS0 P--

RS1RS0Register BankByte Address of R0-R7

0 0000H-07H

0 1108H-0FH

1 0210H-17H

1 1318H-1FH

CPSW.7Cờnhớ

ACPSW.6Cờnhớphụ

--PSW.5Available to user for general purpose

RS1PSW.4Bit chọndãythanhghi1

RS0PSW.3Bit chọndãythanhghi0

OVPSW.2Cờtràn

--PSW.1Dựtrữ-User define bit

PPSW.0Cờchẵnlẻ

Địachỉbit

D0D1D2D3D4D5D6D7

![Ngân hàng câu hỏi thi giữa kì môn Truyền động điện [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/42601758354546.jpg)

![Câu hỏi ôn tập Quy trình an toàn điện có đáp án [kèm đáp án chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/18761758354548.jpg)

![Đề thi trắc nghiệm Kỹ thuật mạch điện tử: Tổng hợp [Năm]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/23481758356189.jpg)

![Tài liệu ôn tập Thông tin quang [năm] [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250917/anvunguyen0207@gmail.com/135x160/56551758168054.jpg)