12. Kh i so sánh t ng t (ANALOG)ố ươ ự

Kh i so sánh t ng t là m t OP AMP so sánh có ngõ vào d ng AIN0 (PB2) và ngõ vào âm AIN1ố ươ ự ộ ươ

(PB3). Khi đi n áp AIN0 l n h n AIN1 ng ra b so sánh s b ng 1. Ngõ ra c a b so sánh có th sệ ớ ơ ỏ ộ ẽ ằ ủ ộ ể ử

d ng làm tác đ ng Capture cho Timer/Counter 1. Ngoài ra b so sánh còn có ch năng yêu c u ng t riêng,ụ ộ ộ ứ ầ ắ

tác đ ng so sánh có th b ng c nh lên, c nh xu ng ho c khi đ i tr ng thái. S đ kh i c a b so sánhộ ể ằ ạ ạ ố ặ ổ ạ ơ ồ ố ủ ộ

mô trên hình 1.25.

Thanh ghi đi u khi n và tr ng thái b so sánh t ng t - ACề ể ạ ộ ươ ự SR

• Bit 7 - ACD: Analog Comparator Disable

Khi ACD = 1 ngu n c a b so sánh bit ng t, bit này có th xoá b t c th i đi m nào đ t t b soồ ủ ộ ắ ể ấ ứ ờ ể ể ắ ộ

sánh t ng t . Khi thay đ i ACD c n c m ng t so sánh t ng t b ng cách xoá bit ACIE trong thanh ghiươ ự ổ ầ ấ ắ ươ ự ằ

ACSR, n u không mu n kích ho t ch ng trình ng t.ế ố ạ ươ ắ

• Bit 6 - Res: Reserved bit

Bit này không s d ng luôn có giá tr b ng 0.ử ụ ị ằ

• Bit 5 - ACO: Analog Comparator Output

ACO n i tr c ti p t ngõ ra c a b so sánh t ng t .ố ự ế ơớ ủ ộ ươ ự

• Bit 4 - ACI: Analog Comparator Interrupt Flag

ACI = 1 khi ngõ ra b so sánh tác đ ng trong ch đ ng t đ c đ nh nghĩa b ng các bit ACI1 vàộ ộ ế ộ ắ ượ ị ằ

ACI0. Ch ng trình ng t so sánh t ng t s đ c g i khi ACIE = 1 và bit I trong SREG = 1. Bit ACI tươ ắ ươ ự ẽ ượ ọ ự

đ ng xoá b ng ph n c ng khi ng t đ c th c hi n. Ngoài ra ACI cũng có th xoá b ng cách ghi vào nóộ ằ ầ ứ ắ ượ ự ệ ể ằ

logic 0.

• Bit 3 - ACIE: Analog Comparator Interrupt Enable

Khi ACIE = 1 và I = 1 ng t so sánh t ng t s đ c cho phép.ắ ươ ư ẽ ượ

• Bit 2 - ACIC: Analog Comparator Input Capture Enable

ACISC = 1 s cho phép ngõ ra b so sánh t ng t tác đ ng capture cho Timer/Counter1. Đ choẽ ộ ươ ự ộ ể

phép ng t ngõ vào Capture Timer/Counter1 c n ph i l p bit TICIE1 trong thanh ghi TIMSK.ắ ấ ả ậ

• Bits 1,0 - ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

Các bit này đ nh nghĩa các tác đ ng ng t khác nhau nh trong b ng sau:ị ộ ắ ư ả

ACIS1 ACIS0 Tác đ ng ng tộ ắ

00 Tác đ ng khi đ i tr ng thái ngõ ra b so sánhộ ổ ạ ộ

01 Không s d ngử ụ

10 Tác đ ng khi ngõ ra có c nh lênộ ạ

11 Tác đ ng khi ngõ ra có c nh xu ngộ ạ ố

Chú ý: Khi thay đ i giá tr các bit ACIS1/ACIS0, c n ph i c m ng t b ng cách xoá bit cho phép ng tổ ị ầ ả ấ ắ ằ ắ

trong thanh ghi ACSR, n u không ng t s x y ra khi các bit thay đ i giá tr . Khi s d ng các l nh SBIế ắ ẽ ả ổ ị ử ụ ệ

ho c CBI v i các bit khác trong thanh ghi ACSR cũng có th ghi giá tr 1 vào thanh ghi ACI, nên c n ph iặ ớ ể ị ầ ả

ki m tra l i, n u nó b ng 1 c n xoá nó đi.ể ạ ế ằ ầ

13. B bi n đ i t ng t sang s (ADC).ộ ế ổ ươ ự ố

B ADC c a MCU AT90S8535 có các đ c tính chính nh sau:ộ ủ ặ ư

• Đ phân gi i 10-bit.ộ ả

• Đ chính xác ±2 LSB.ộ

• Tích phân không tuy n tính 0.5 LSB.ế

• Th i gian bi n đ i 65 - 260 μs.ờ ế ổ

• Có 8 ngõ vào Multiplexed.

• D i ngõ vào Rail-to-Rail.ả

• Có các ch đ bi n đ i Free Run ho c Single.ế ộ ế ổ ặ

• Có ng t hoàn thành bi n đ i.ắ ế ổ

• Có ch đ ng ch ng nhi u.ế ộ ủ ố ễ

ADC c a AT90S8535 là lo i x p x liên ti p 10 bit, v i 8 ngõ vào ch n b ng ph n m m m i ngõ sủ ạ ấ ỉ ế ớ ọ ằ ầ ề ỗ ẽ

t ng ng v i 1 c ng c a PORT A. Ngõ vào ADC có b khu ch đ i l y và gi m u đ m b o cho đi nươ ứ ớ ổ ủ ộ ế ạ ấ ữ ẫ ả ả ệ

áp ngõ vào luôn b ng h ng s trong su t quá trình bi n đ i. S đ kh i c a b ADC đ c mô t trênằ ằ ố ố ế ổ ơ ồ ố ủ ộ ượ ả

hình 1.26.

ADC có hai ngu n cung c p riêng, AVCC và AGND. Chân AGND c n n i GND còn AVCC khôngồ ấ ầ ố

nên sai khác qua 0.3V so v i VCC. Ngoài ra c n ph i cung c p ngu n chu n t i chân AREF,ớ ầ ả ấ ồ ẩ ớ đi n áp nàyệ

c n n m trong kho ng AGND – AVCC.ầ ằ ả

Ho t đ ng.ạ ộ

ADC có th ho t đ ng m t trong hai ch đ Single và free run. Trong ch đ single ng i sể ạ ộ ở ộ ế ộ ế ộ ườ ử

d ng s kh i đ ng các chu kỳ bi n đ i. Trong ch đ Free Run, ADC s t đ ng l y các m u bi n đ iụ ẽ ở ộ ế ổ ế ộ ẽ ự ộ ầ ẫ ế ổ

theo các th i h ng c đ nh sau đó c p nh t thông tín vào Thanh ghi d li u c a nó. Bit ADFR trongờ ằ ố ị ậ ậ ữ ệ ủ

ADCSR s chuy n đ i ho t đ ng c a ADC gi a hai ch đ này.ẽ ể ổ ạ ộ ủ ữ ế ộ

Đ cho phép kh i ADC ho t đ ng c n ghi 1 t i bit ADEN trong ADCSR. Chu kỳ bi n đ i đ uể ố ạ ộ ầ ớ ế ổ ầ

tiên s b t đ u ngay sau khi ADEN = 1, tuy nhiên th i gian th c hi n s dài h n thông th ng 12 chu kỳẽ ắ ầ ờ ự ệ ẽ ơ ườ

clock do quá trình kh i đ ng ADC.ở ộ

M t chu kỳ bi n đ i s b t đ u b ng cách ghi logic 1 t i bit kh i3 đ ng quá trình bi n đ iộ ế ổ ẽ ắ ầ ằ ớ ờ ộ ế ổ

ADSC,bit nay s gi nguyên m c cao trong su t chu kỳ bi n đ i, và t đ ng đ c xoá b ng ph n c ngẽ ữ ứ ố ế ổ ự ộ ượ ằ ầ ứ

khi quá trình bi n đ i k t thúc. N u m t ngõ vào khác đ c ch n trong quá trình bi n đ i, ADC s ti pế ổ ế ế ộ ượ ọ ế ổ ẽ ế

t c th c hi n xong tr c khi chuy n qua bi n đ i giá tr trên kênh m i.ụ ự ệ ướ ể ế ổ ị ớ

10 bit k t qu bi n đ i do ADC t o ra s đ c ghi vào các thanh ghi ADCH và ADCL. C n th cế ả ế ổ ạ ẽ ượ ầ ự

hi n m t c ch logic b o v d li u s đ m b o n i dung các thanh ghi không b bi n đ i trong khiệ ộ ơ ế ả ệ ữ ệ ẽ ả ả ộ ị ế ổ

đ c, c ch đó nh sau:ọ ơ ế ư

C n ph i đ c ADCL tr c, m i khi đ c ADCL các thanh ghi d li u s đ c khoá l i, nh v yầ ả ọ ướ ỗ ọ ữ ệ ẽ ượ ạ ư ậ

n u quá trình bi n đ i k t thúc tr c khi đ c ADCH thì không có thanh ghi d li u nào b thay đ i vàế ế ổ ế ướ ọ ữ ệ ị ổ

k tqu bi n đ i s không b m t. Sau khi đ c ADCH, c ADCL và ADCH s đ c cho phép ghi tr l i.ế ả ế ổ ẽ ị ấ ọ ả ẽ ượ ở ạ

ADC cũng có m t ng t riêng, bit ADIF s đ c l p sau khi quá trình bi n đ i hoàn thành, khi truyộ ắ ẽ ượ ậ ế ổ

c p các thanh ghi d li u không đúng, yêu c u ng t v n đ c duy trì ngay c khi d li u b m t.ậ ữ ệ ầ ắ ẫ ượ ả ữ ệ ị ấ

B ti n chia clock c a ADC.ộ ề ủ

ADC s d ng m t b ti n chia clock có ch c năng chia clock h th ng đ cung c p cho ho tử ụ ộ ộ ề ứ ệ ố ể ấ ạ

đ ng bi n đ i c a nó. T n s clock c a ADC trong kho ng t 50 – 200 kHz. Khi s d ng t n s càngộ ế ổ ủ ầ ố ủ ả ừ ử ụ ầ ố

cao, đ chính xác s càng gi m.ộ ẽ ả

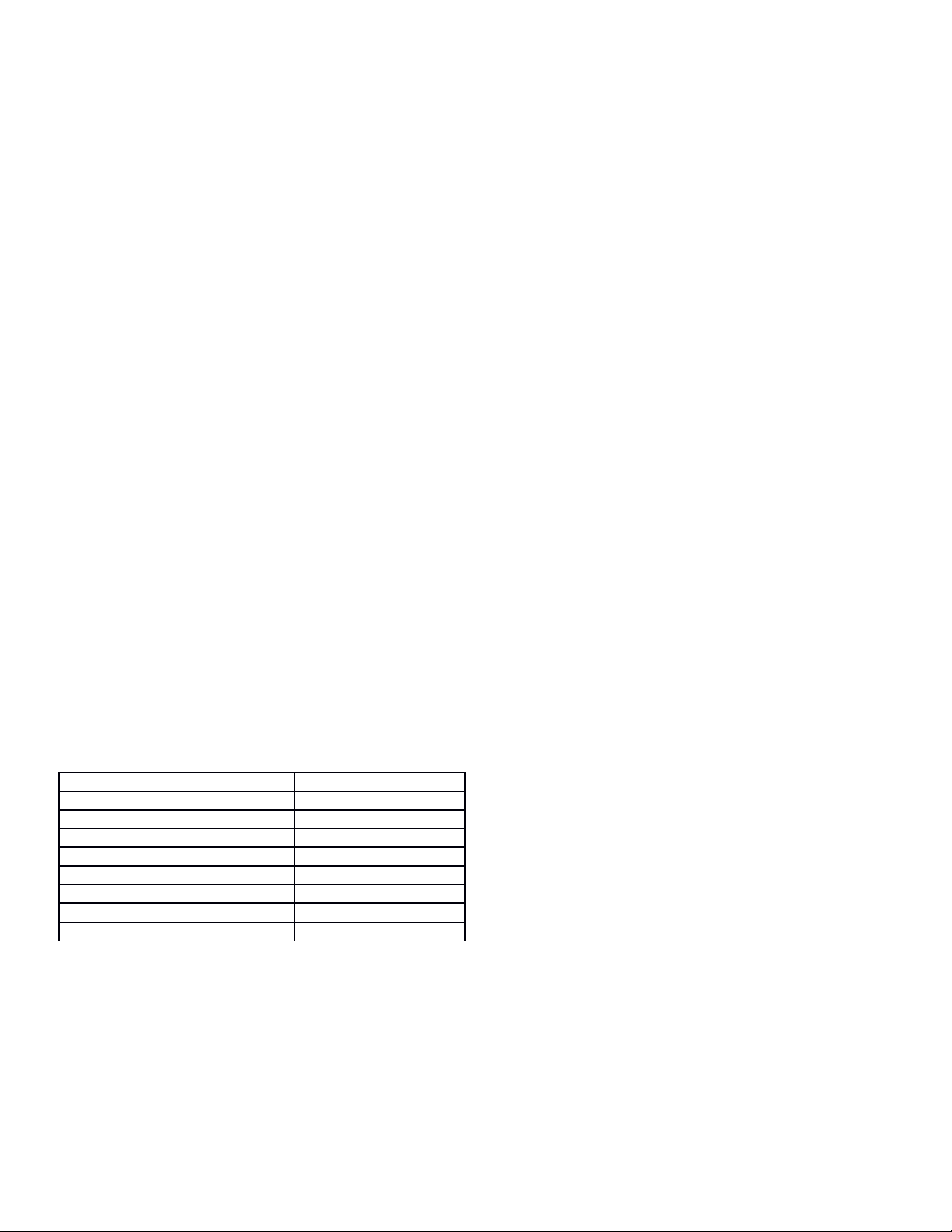

Các bit ADPS0 - ADPS2 trong ADCSR đ c s d ng đ t o ra t n s clock thích h p cho ADC tượ ử ụ ể ạ ầ ố ợ ừ

b t các th ch anh có t n s trên 100 kHz. B ti n chia s ho t đ ng ngay sau khi ADEN = 1,và nó sấ ạ ầ ố ộ ề ẽ ạ ộ ẽ

reset khi ADEN = 0.

Khi l p ADSC = 1 quá trình bi n đ i s b t đ u t i c nh lên ti p theo c a chu kỳ clock ADC.ậ ế ổ ẽ ắ ầ ạ ạ ế ủ

Quá trình l y m u và gi s chi m kho ng 1.5 clock ADC sau khi quá trình bi n đ i b t đ u.K t quấ ẫ ữ ẽ ế ả ế ổ ắ ầ ế ả

s đ c ghi vào các thanh ghi d li u sau 13 chu kỳ clock. Trong ch đ Single ADC c n ch thêm ítẽ ượ ữ ệ ế ộ ầ ờ

nh t m t chu kỳ clock tr c khi th c hi n chu kỳ bi n đ i ti p theo (hình 1.28). N u ADSC = 1, ADCấ ộ ướ ự ệ ế ổ ế ế

s l p t c th c hi n chu kỳ bi n đ i m i. Trong ch đ Free Run v i t n s clock cao nh t 200 kHz sẽ ậ ứ ự ệ ế ổ ớ ế ộ ớ ầ ố ấ ẽ

cho th i gian bi n đ i th p nh t là 65ms t ng đ ng v i 15.4 kSPS. Th i gian bi n đ i các giaiờ ế ổ ấ ấ ươ ươ ớ ờ ế ổ ở

đo n c a các ch đ khác nhau cho trong b ng sau:ạ ủ ế ộ ả

Ch đế ộ S chu kỳố

l y m uấ ẫ S chu kỳ đ d li uố ể ữ ệ

s n sàngẵT ng th i gian bi nổ ờ ế

đ i (chu kỳ)ổT ng th i gian bi nổ ờ ế

đ i (ổs)

Chu kỳ đ u tiên trong ch đ Freeầ ế ộ

Run

14 25 25 125 – 500

Chu kỳ đ u tiên trong ch đ Singleầ ế ộ 14 25 26 130 – 520

Chu kỳ thông th ng trong ch đườ ế ộ

Free Run

2 13 13 65 – 260

Chu kỳ thông th ng trong ch đườ ế ộ

Single

2 13 14 70 - 280

Ch c năng ch ng nhi u ADC.ứ ố ễ

Ch c năng ch ng nhi u c a ADCcho phép quá trình bi n đ i th c hi n trong ch đ Idle v iứ ố ễ ủ ế ổ ự ệ ế ộ ớ

ch c năng gi m thi u nhi u bao g m c nhi u t CPU. Đ th c hi n ch c năng này c n th c hi n cácứ ả ể ễ ồ ả ễ ừ ể ự ệ ứ ầ ự ệ

b c sau:ướ

1. ADC đã đ c ch n và không đang trong quá trình bi n đ i. Ch n ch đ Single và cho pheé ng tượ ọ ế ổ ọ ế ộ ắ

ADC.

ADEN = 1

ADSC = 0

ADFR = 0

ADIE = 1

2. Chuy n qua ch đ idle, ADC s b t đ u bi n đ i khi CPU ng ng ho t đ ng.ể ế ộ ẽ ắ ầ ế ổ ư ạ ộ

3. N u không có ng t nào x y ra tr c khi quá trình bi n đ i ADC hoàn thành, ng t ADC s đánhế ắ ả ướ ế ổ ắ ẽ

th c MCU và th c hi n ch ng trình ng t ph c v vi c x lý d li u bi n đ i.ứ ự ệ ươ ắ ụ ụ ệ ử ữ ệ ế ổ

Thanh ghi chon ngõ vào ADC - ADMUX

• Bits 7..3 - Res: Reserved Bits

Các bit này không s d ng và luôn có giá tr b ng 0.ử ụ ị ằ

• Bits 2..0 - MUX2..MUX0: Analog Channel Select Bits 2-0

Giá tr các bit này s ch n các ngõ vào t ng ng t 0 -7 c a ADC.ị ẽ ọ ươ ứ ừ ủ

ADC Control and Status Register - ADCSR

• Bit 7 - ADEN: ADC Enable

ADEN = 1 cho phép ADC ho t đ ng. Khi ADEN = 0 ADC bit c m, n u c m ADC khi đang trongạ ộ ấ ế ấ

chu kỳ bi n đ i, chu kỳ đó s l p t c k t thúc.ế ổ ẽ ậ ứ ế

• Bit 6 - ADSC: ADC Start Conversion

Trong ch đ Single ADSC= 1 s kh i đ ng quá trình bi n đ i. Trong ch đ Free Run ADSC = 1ế ộ ẽ ở ộ ế ổ ế ộ

s kh i đ ng chu kỳ bi n đ i đ u tiên. L n đ u tiên ghi ADSC =1 sau khi ADEN = 1 (ho c đ ng th iẽ ở ộ ế ổ ầ ầ ầ ặ ồ ờ

v i ADEN = 1), ADC s đ c kh i đ ng. ADSC = 1 trong su t quá trình bi n đ i và s b ng 0 khi quáớ ẽ ượ ở ộ ố ế ổ ẽ ằ

trình bi n đ i k t thúc tr c khi k t qu bi n đ i ghi t i các thanh ghi d li u c a nó,ế ổ ế ướ ế ả ế ổ ớ ữ ệ ủ đi u này choề

phép b t đ u m t chu kỳ bi n đ i m i tr c khi chu kỳ bi n đ i hi n hành hoàn t t. ắ ầ ộ ế ổ ớ ướ ế ổ ệ ấ

• Bit 5 - ADFR: ADC Free Run Select

Khi ghi ADFR = 1 ADC s ho t đ ng trong ch đ Free Run. Trong ch đ này ADC s l y mẽ ạ ộ ế ộ ế ộ ẽ ấ ẫ

bi n đ i và c p nh t giá tr cho các thanh ghi d li u m t cách liên t c.ế ổ ậ ậ ị ữ ệ ộ ụ

• Bit 4 -ADIF: ADC Interrupt Flag

ADIF = 1 khi đang th c hi n ch ng trình ng t ADC, ch ng trình ng t s th c hi n khi k t quự ệ ươ ắ ươ ắ ẽ ự ệ ế ả

bi n đ i đ c chuy n t i các thanh ghi d li u và tr c đó ADIE = 1, I = 1. ADIF s t đ ng xoá b ngế ổ ượ ể ớ ữ ệ ướ ẽ ự ộ ằ

ph n c ng khi th c hi n ch ng trình ng t t ng ng. Ngoài ra ADIF cũng có th xoá b ng l nh.ầ ứ ự ệ ươ ắ ươ ứ ể ằ ệ

• Bit 3 - ADIE: ADC Interrupt Enable

ADIE = 1 và I= 1 cho phép ng t ADC. ắ

• Bits 2..0 - ADPS2..ADPS0: ADC Prescaler Select Bits

Các bit xác đ nh h s c a b ti n chia trong ADC.ị ệ ố ủ ộ ề

ADPS2 ADPS1 ADPS0 H s chiaệ ố

000 1

001 2

010 4

011 8

100 16

101 32

110 64

111 128

Thanh ghi d li u ADC - ADCL và ADCHữ ệ

Thanh ghi này ch a k t qu bi n đ i ADC. Trong ch đ Free Run c n ph i đ c ADCL tr cứ ế ả ế ổ ế ộ ầ ả ọ ướ

ADCH.

Quét nhi u kênh. ề

Do s chuy n ự ể kênh vào luôn ph i ch cho đ n khi quá trình bi n đ i k t thúc, ch đ Free Run cóả ờ ế ế ổ ế ế ộ

th s d ng đ quét đ ng th i nhi u kênh vào mà không c n d ng quá trình bi n đ i. Thông th ngể ử ụ ể ồ ờ ề ầ ừ ế ổ ườ

ng t k t thúc bi n đ i ADC s s d ng đ đ i kênh vào. Tuy nhiên ng i s d ng cũng có th th cắ ế ế ổ ẽ ử ụ ể ổ ườ ử ụ ể ự

hi n vi c chuy n đ i kênh nh sau:ệ ệ ể ổ ư

Khi có tác đ ng ng t k t qu bi n đ i đã s n sàng, n u ADMUX đ c thay đ i giá tr ngay sauộ ắ ế ả ế ổ ẵ ế ượ ổ ị

khi có tác đ ng ng t quá trình bi n đ i m i s s n sàng v i các thi t l p ADC nh cũ.ộ ắ ế ổ ớ ẽ ẵ ớ ế ậ ư

K thu t lo i nhi u ADC.ỹ ậ ạ ễ

Các m ch đi n s bên trong và bên ngoài MCU có th tác đ ng t i đ chính xác quá trình bi nạ ệ ố ể ộ ớ ộ ế

đ i t ng t . Khi c n đ chính xác l n, chúng ta có th gi m nh h ng nhi u nh sau:ổ ươ ự ầ ộ ớ ể ả ả ưở ễ ư

1. Các kh i li n quan t i tín hi u t ng t c a MCU và t t c các linh ki n liên quan t i tín hi uố ệ ớ ệ ươ ự ủ ấ ả ệ ớ ệ

t ng t khác c n ph i có đ ng mass 1 l p riêng trên m ch in. Mass t ng t ch n i v iươ ự ầ ả ườ ở ớ ạ ươ ự ỉ ố ớ

mass s b ng m t đi m xuyên l duy nh t (via).ố ằ ộ ể ỗ ấ

2. T o đ ng n i tín hi u t ng t ng n nh t có th , đ m b o đ ng tín hi u t ng t ch y songạ ườ ố ệ ươ ự ắ ấ ể ả ả ườ ệ ươ ự ạ

song v i mass c a nó l p ngu n và tránh xa các đ ng truy n d li u s có t c đ chuy nớ ủ ở ớ ồ ườ ề ữ ệ ố ố ộ ể

m ch cao.ạ

3. Chân AVCC c a MCU c n n i t i ngu n cung c p s VCC thông qua m ch RC nh hình 1.28.ủ ầ ố ớ ồ ấ ố ạ ư

4. S d ng ch c năng lo i nhi u ADC đ gi m nhi u nh h ng t CPU.ử ụ ứ ạ ễ ể ả ễ ả ưở ừ

5. N u m t chân c ng A đ c s d ng làm ngõ vào ra s thì nên tránh tác đ ng chuy n tr ng tháiế ộ ổ ượ ử ụ ố ộ ể ạ

c a nó trong chu kỳ bi n đ i ADC.ủ ế ổ

. Các c ng vào ra s .ổ ố

T t c các c ng vào ra s c a AVR đ u có ch c năng Đ c – Thay đ i – Ghi (Read-Modify-ấ ả ổ ố ủ ề ứ ọ ổ

Write), có nghĩa là h ng truy n trên m t chân vào ra mà không nh h ng t i h ng vào ra c a cácướ ề ộ ả ưở ớ ướ ủ

chân vào ra khác b ng các l nh SBI và CBI. Chúng ta có th l p t c thay đ i giá tr đ nh nghĩa vào ra choằ ệ ể ậ ứ ổ ị ị

c ng ho c c m/cho phép đi n tr kéo lên ngu n cho các ngõ vào.ổ ặ ấ ệ ở ồ

C ng Aổ

C ng A là m t c ng vào ra 2 chi u 8 bit, có 3 đ a ch trong vùng đ a ch vào ra đ c s d ng choổ ộ ổ ề ị ỉ ị ỉ ượ ử ụ

c ng A bao g m: Thanh ghi d li u cho c ng A (PORTA - $3B), thanh ghi đ nh h ng truy n cho c ng Aổ ồ ữ ệ ổ ị ướ ề ổ

(DDRA - $3A) và thanh ghi các chân vào c ng A (PINA - $39). Thanh ghi PINA là thanh ghi ch đ c, haiổ ỉ ọ

thanh ghi còn l i có th đ c ghi. T t c các chân vào c ng A đ u có th ch n đi n tr Pull – Up. Bạ ể ọ ấ ả ổ ề ể ọ ệ ở ộ

đ m ngõ ra c ng A có th cung c p dòng 20 mA đ cung c p dòng kép LED tr c ti p. Khi c ng A đ cệ ổ ể ấ ể ấ ự ế ổ ượ

l p trình là ngõ vào và bên ngoài đ c kéo xu ng th p, chúng tr thành ngu n dòng khi ch n đi n trậ ượ ố ấ ở ồ ọ ệ ở

Pull – Up bên trong. Khi đ c d li u t c ng A, là đ c thanh ghi d li u c ng A (PORT A) là b nhọ ữ ệ ừ ổ ọ ữ ệ ổ ộ ớ

đ m c ng A. Còn khi đ c PINA là đ c tr ng thái v t lý th c s trên c ng A.ệ ổ ọ ọ ạ ậ ự ự ổ

C ng A có th chuy n qua ch c năng là các ngõ vào cho b ADC, n u m t trong các ngõ vào c ngổ ể ể ứ ộ ế ộ ổ

A v n gi ch c năng vào ra, c n ph i tránh tác đ ng thay đ i tr ng thái trong khi ADC đang trong chu kỳẫ ữ ứ ầ ả ộ ổ ạ

bi n đ i, tác đ ng này có th làm thay đ i k t qu bi n đ i ADC.ế ổ ộ ể ổ ế ả ế ổ

![Bài giảng Nhập môn Kỹ thuật điện [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251208/nguyendoangiabao365@gmail.com/135x160/60591765176011.jpg)

![Bài giảng Cảm biến và ứng dụng: Chương 1 - Các khái niệm và đặc trưng cơ bản [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251204/kimphuong1001/135x160/51101764832169.jpg)