1

Đề cương kỹ thuật xung số - B3DT1

mục lục

Câu 1: các định lý cơ bản của đại số Boolean ............................................ 2

Câu 2 : các công thức loogic cơ bản ............................................................. 3

Câu 3: đơn giản biểu thức .............................................................................. 4

Câu 4: thiết kế mạnh logic ............................................................................. 6

Câu 5 các mạnh mã hóa................................................................................ 10

Câu 6: các mạch giải mã ............................................................................... 12

Câu 7: mạch hợp kênh và phân kênh ........................................................ 14

Câu 8: Các mạch số học................................................................................ 18

Câu 9: Các mạch Flip - Flop cơ bản .......................................................... 23

Câu 10: các loại mạch đếm .......................................................................... 31

Câu 11: mạch chốt và ghi dịch. ................................................................... 37

Câu 12: bộ biến đổi DAC.............................................................................. 41

Câu 13: bộ biến đổi ADC.............................................................................. 44

Câu 14: mạch tạo xung dùng 2 cổng NAND............................................ 52

Câu 15: Mạch tạo xung dùng IC 555 ......................................................... 53

2

Câu 1: các định lý cơ bản của đại số Boolean

+ các mệnh đề cơ sở

X + -

X = 1

X . -

X = 0

X + 1 = 1

X . 1 = X

+ Định luật hấp thụ

X + X = X

X . X = X

+ Định luật phủ định của phủ định.

XX

+ Định luật kết hợp

321321 )()( XXXXXX

)..()..( 321321 XXXXXX

+ định luật giao hoán.

X1 + X2 = X 2 + X1

X1 . X2 = X2 .X1

+ Định luật phân phối

3121321 ).( XXXXXXX

3213121 .))((XXXXXXX

+Định luật DEMORGAN

2121 XXXX

2121 .XXXX

3

Câu 2 : các công thức loogic cơ bản

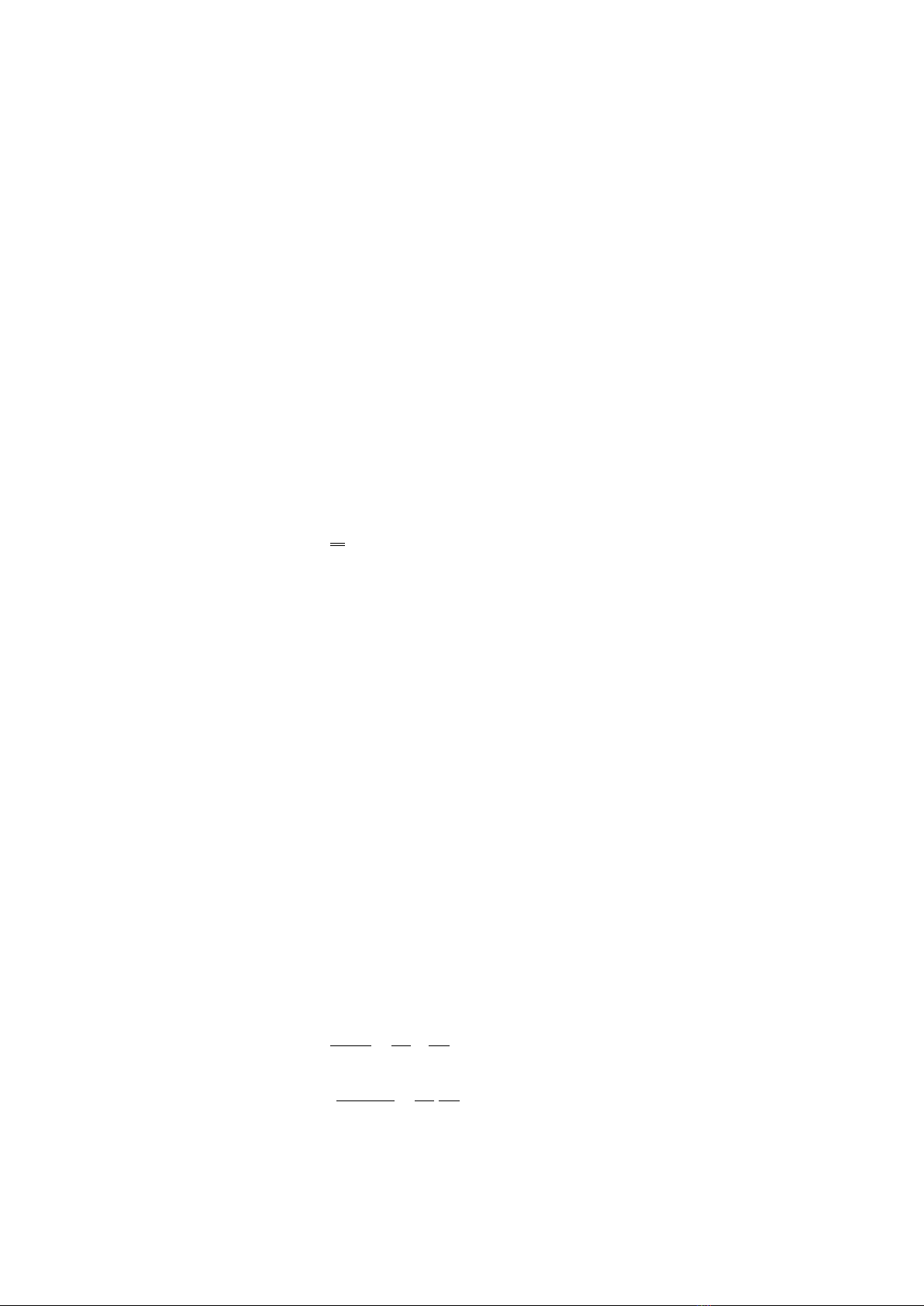

+ phép cộng logic - hàm hoặc (OR)

Y = X1 + X2

Y

X1

X2

+ Phép nhân logic - hàm và (AND)

Y = X1 . X2

X1

X2

Y

+Phép phủ định - hàm đảo ( NOT)

Y = -

X

X Y

+ Hàm không hoặc ( NOR)

21 XXY

Y

X

1

X

2

+ Hàm không và ( NAND)

21.XXY

X

1

X

2

Y

4

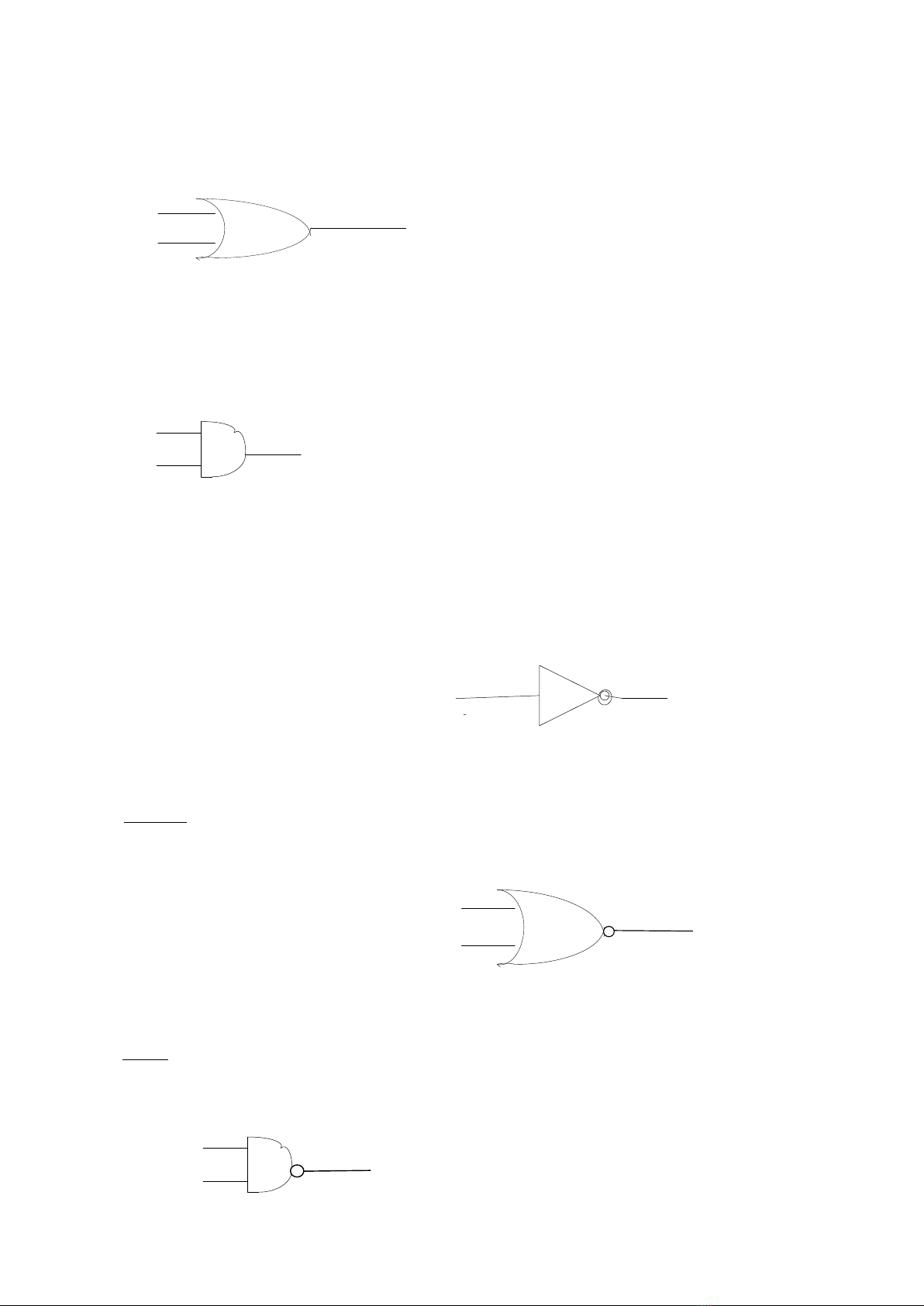

+ Hàm hoặc tuyệt đối 2 đầu vào

Y = X1 .-

X2 + -

X1.X2

Được viết lại là: y = X1

+

X2

Y

X1

X2

+Hàm không hoặc tuyệt đối (xnor)

21 XXY

Y

X1

X2

Câu 3: đơn giản biểu thức

* trường hợp xây dựng hàm logic theo phương pháp giải tích:

- ta áp dụng các định luật của đại số logic để đơn giản hàm logic sao cho hàm cuối

cùng là tối giản, thực hiện hàm cần ít phần tử logic cơ bản nhất

*trường hợp xây dựng hàm logic từ bảng karnaugh

- ta hãy ghép các minterm ứng với f1 = 1 (các ô có số 1) ở các ô kề nhau theo hàng

ngang hoặc hàng dọc và ghép các ô bằng 1 nằm đối diện nhau trong bảng như các

đường khoanh vòng tròn trong hình 1. các minterm được ghép như vậy nhất định sẽ

có thừa số chung và sẽ đơn giản được 1 biến bù nhau.

1

1

A

B

01

0

11

1

1

0

1

C

AB

00 01 1011

1

F = -

A B + A -

B F = -

A -

B -

C + -

A -

B C + A -

B -

C + A B C

hình a, hình b,

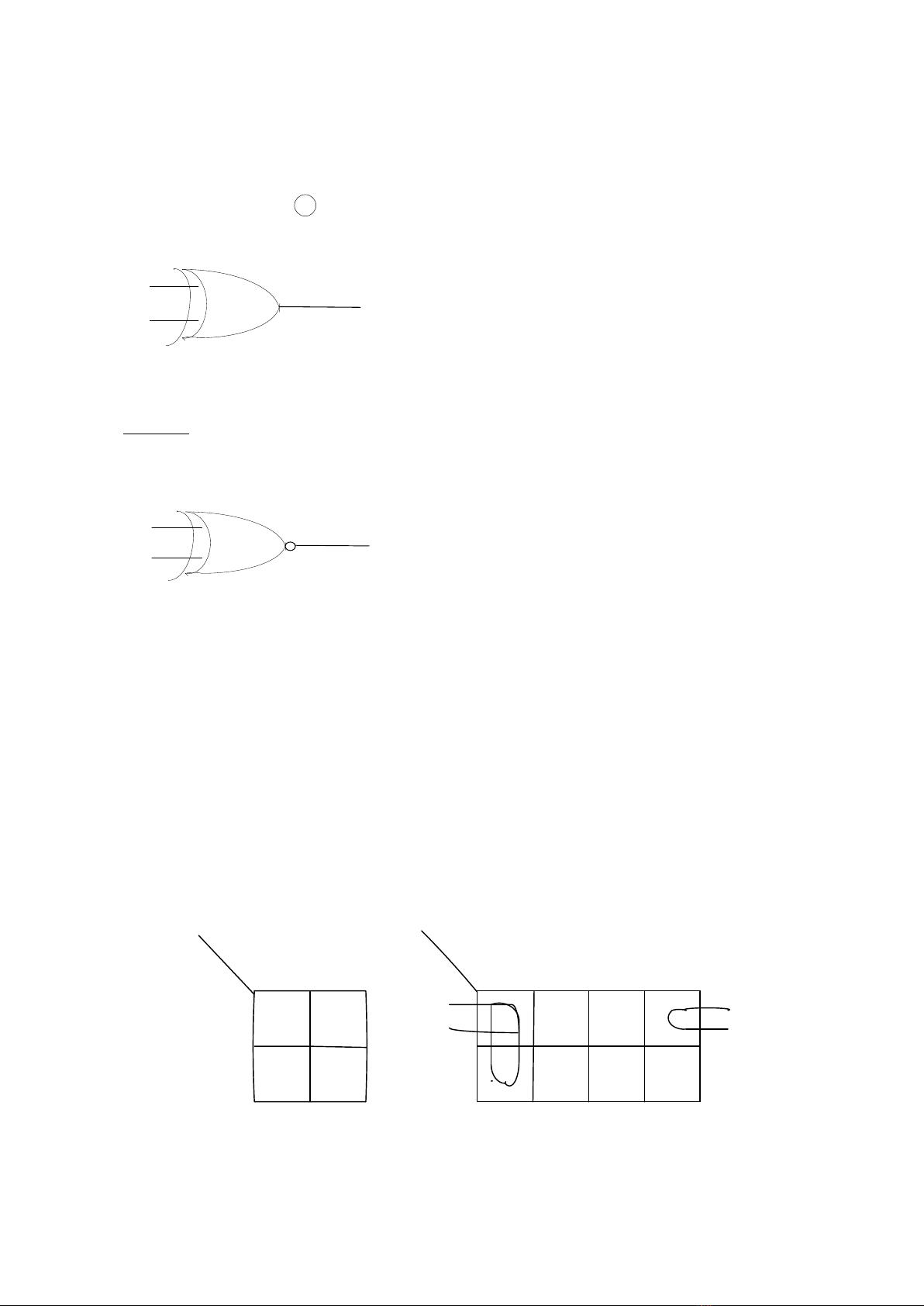

5

1

1

1

1

AB

CD 00 01 11 10

00

01

11

10

1

11

1

1

AB

CD 00 01 11 10

00

01

11

10

F= -

A-

B-

C-

D+ -

AB-

CD+A-

BCD+A-

BC -

D F =AB -

C-

D+A-

B-

C-

D+ -

A-

BCD+-

A-

BC -

D+A-

BC -

D

hình C, hình d,

- hinh b ta có:

F = -

A -

B -

C + -

A -

B C + A -

B -

C + A B C ghép 2 minterm kề nhau

F = -

A -

B ( -

C +C) + -

A-

BC + A -

B -

C +ABC vì -

C +C =1

F = -

A -

B + A-

B -

C + ABC

Để đơn giản 2 ô đối diện, ở đây ta viết thêm số hạng -

A -

B -

C và hàm F vẫn không thay

đổi ( vì -

A -

B -

C + -

A -

B -

C )= -

A -

B -

C ta có:

F = -

A -

B + A B C + A -

B -

C + -

A -

B -

C ghép 2 số hạng cuối:

F = -

A -

B +A B C + -

B -

C( A + -

A) cuối cùng:

F = -

A -

B + A B C + -

B -

C

- Hình d ta có:

Hàm F có số hạng -

A-

BC -

D cộng thêm -

A-

BC -

D vẫn không đổi:

F = AB-

C-

D + A-

B-

C-

D + -

A-

BCD + -

A-

BC -

D + -

A-

BC -

D

F = A-

C-

D (B+ -

B ) + -

A-

BC (D+ -

D) + -

BC -

D (A + -

A)

F = A-

C-

D + -

A-

BC + -

BC -

D

![Giáo trình Điện tử số Phần 2: [Mô tả nội dung phần 2, ví dụ: Mạch logic, Thiết kế mạch,...]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260305/hoatulip2026/135x160/87191773135922.jpg)

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Vô tuyến điện viên hàng hải GMDSS hạng tổng quát: Phần 1 [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/45101777969769.jpg)