Ghép nối và điều khiển thiết bị ngoại vi (P2)

lượt xem 14

download

Download

Vui lòng tải xuống để xem tài liệu đầy đủ

Download

Vui lòng tải xuống để xem tài liệu đầy đủ

Tín hiệu OBF chuyển về mức thấp để thông báo rằng CPU đã ghi dữ liệu ra một công thức xác định .Tín hiệu OBF F/F sẽ được xác lập ở sườn lên của tín hiệu WR và bị xóa khi tín hiệu vào ACK ở mức thấp

Bình luận(0) Đăng nhập để gửi bình luận!

Nội dung Text: Ghép nối và điều khiển thiết bị ngoại vi (P2)

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi Các tín hi u ñi u khi n ra ñư c dùng trong ch ñ ra • OBF ( Output Bufer Full F/F). Tín hi u ra OBF chuy n v m c th p ñ thông báo r ng CPU ñã ghi d li u ra m t c ng xác ñ nh. Tín hi u OBF F/F s ñư c xác l p sư n lên c a tín hi u WR và b xoá khi tín hi u vào ACK m c th p . • ACK (Acknowledge Input ). M c th p c a tín hi u vào này thông báo cho 8255 r ng d li u t c ng A ho c c ng B ñã ñư c ch p nh n. V b n ch t ñây là tín hi u phúc ñáp t thi t b ngo i vi thông báo nó ñã nh n ñư c d li u g i t i t CPU. • INTR (Interrupt Request ) M c cao c a tín hi u ra này ñư c s d ng ñ yêu c u ng t CPU khi m t thi t b ngoài ñã nh n ñư c d li u truy n t CPU. Tín hi u INTR xác l p khi tín hi u ACK = "1", OBF = "1" và INTE ="1" . Tín hi u này ñư c kh i t o l i sư n xu ng c a tín hi u WR . Các t l nh c a ch ñ này như sau: * Ð th th i gian c a ch ñ ho t ñ ng này như sau : Gi ng viên: Nguy n Văn Minh Trí 31

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi Ð th th i gian quá trình ghi. Trong ch ñ 1, hai c ng A và B có th ñư c l p trình m t cách riêng bi t là c ng vào ho c c ng ra ñ ho t ñ ng trong các ng d ng vào /ra có h i tho i khác nhau. Các t l nh ho t ñ ng trong ch ñ này như sau: 3. Ch ñ 2 Ch ñ ho t ñ ng này cung c p kh năng trao ñ i d li u v i các thi t b ngo i vi s d ng m t ñư ng truy n 8 bit ñ v a truy n v a nh n d li u (Bus vào/ra hai chi u). Các tín hi u h i tho i ñư c dùng trong ch ñ này ñ ñi u khi n vi c truy n d li u cũng tương t như ch ñ 1. Các ch c năng cơ b n c a ch ñ 2: Gi ng viên: Nguy n Văn Minh Trí 32

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi - Trong ch ñ này ch có nhóm A ñư c s d ng . - C ng A là c ng vào/ ra hai chi u 8 bit . - Các tín hi u vào/ra ñ u ñư c ch t l i. - 5 bit c a c ng C ñư c s d ng làm c ng ñi u khi n ,tr ng thái cho c ng A 8 bit. Các tín hi u ñi u khi n ra . • OBF( Output buffer full ) Tín hi u ra OBF m c th p thông báo CPU khi d li u ra c ng A. • ACK (Acknowledge) M c th p c a tín hi u vào này cho phép b ñ m ra bus d li u c a c ng A g i d li u. Ngư c l i, b ñ m ra này s tr ng thái tr kháng cao . • INTE 1 ( Tín hi u INTE ph i h p v i tín hi u OBF ). Ði u khi n b i vi c l p bit ho c xoá bit PC4 . Các tín hi u ñi u khi n vào . • STB (Srobe input ). M c th p c a tín hi u vào này ñ c d li u vào c ng vào ch t . • IBF ( Input bufer Full ). M c cao c a tín hi u ra này ch ra r ng tín hi u ñã ñư c ghi vào c ng vào ch t . • INTE2 ( Tín hi u INTE ph i h p v i tín hi u IBF) Ði u khi n b i vi c xoá /l p bit c a PC4 Các t l nh ho t ñ ng trong ch ñ này như sau : Gi ng viên: Nguy n Văn Minh Trí 33

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 4. Ch ñ k t h p Ngoài vi c ho t ñ ng riêng r theo t ng ch ñ , 8255 còn có kh năng ho t ñ ng ñ ng th i k t h p các ch ñ khi không ph i t t c các bit trong c ng C ñư c s d ng ñ ñi u khi n ho c dành cho tr ng thái. Các bit còn l i có th ñư c s d ng ñ th c hi n các ch c năng sau : Khi ñư c l p trình là các ñư ng vào tín hi u T t c các ñư ng vào tín hi u ñ u có th ñư c truy c p trong su t quá trình ñ c c ng C thông thư ng. Như trong hình v minh ho sau : Gi ng viên: Nguy n Văn Minh Trí 34

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi Khi ñư c l p trình là các ñư ng tín hi u ra Các bit trong s các bit cao c a c ng C ( PC7- PC4) ph i ñư c truy c p m t cách riêng r b ng cách s d ng ch c năng xoá /l p bit. Các bit trong s các bit th p c a c ng C có th truy c p b ng ch c năng xoá /l p bit ho c dùng 3 bit tương ng ghi ra c ng C . * Ð c tr ng thái c ng C. Trong mode 0, c ng C truy n d li u t i ho c t thi t b ngo i vi. Khi 8255 ñư c l p trình ho t ñ ng trong mode 1 ho c mode 2, c ng C ñư c s d ng ñ t o ra ho c nh n tín hi u h i tho i trao ñ i v i thi t b ngo i vi. Ð c n i dung c a c ng C cho phép ngư i l p trình ki m tra tr ng thái c a các thi t b ngo i vi và ñi u khi n quá trình trao ñ i d li u. Không có l nh ñ c bi t nào dùng ñ ñ c thông tin tr ng thái t c ng C mà ch có thao tác ñ c thông thư ng th c hi n ch c năng này. Gi ng viên: Nguy n Văn Minh Trí 35

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 5. Ch c năng xoá bit và l p bit (single bit set/reset ) B t c bit nào trong 8 bit c a c ng C ñ u có th ñư c thi t l p ho c ñư c xoá nh s d ng các l nh ghi ra thanh ghi ñi u khi n các bit phù h p. Như v y khi c ng C ñang ñư c dùng ñ ñi u khi n, ghi tr ng thái cho c ng A ho c c ng B thì nh ng bit c a c ng C có th ñư c xoá ho c ñư c thi t l p nh s d ng các l nh xoá, thi t l p bit như khi c ng C là c ng ra d li u. - T l nh ho t ñ ng trong ch ñ như sau: Gi ng viên: Nguy n Văn Minh Trí 36

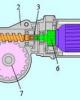

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 6. Ch c năng ñi u khi n ng t (Interrupt control ) Khi 8255 ñư c l p trình ho t ñ ng ch ñ 1 ho c ch ñ 2, các tín hi u ñi u khi n c a nó có th ñư c s d ng như yêu c u ng t t i CPU. Tín hi u yêu c u ng t t o b i c ng C có th b c m hay ñư c phép nh xoá hay xác l p m ch l t INTE s d ng ch c năng l p xoá bit như ñã nêu trên. Ch c năng này cho phép ngư i l p trình có th cho phép ho c không cho phép m t thi t b I/O ng t CPU mà không gây nh hư ng t i b t kỳ m t thi t b nào khác trong c u trúc ng t . 2.3.3 Ghép n i v i 8255A Hình 2.9 trình bày m t ví d m t m ch GN 8255A v i máy in, máy ñ c băng ch ñ 0. N a th p c a C là c a vào, dùng ñ ñ c các tr ng thái - PC1 cho tr ng thái b n c a máy in. - PC0 cho tr ng thái s n sàng c a máy ñ c băng. N a cao c a C là c a ra, dùng ñ ñưa ra tín hi u ñi u khi n: - PC5 ñưa tín hi u ch t s li u cho máy in (qua b ñ o). - PC4 ñ d ch chuy n băng gi y ñi 1 v trí v bên ph i (qua b khu ch ñ i ñ o). Hình 2.10 mô t m ch ghép n i v i máy in ch ñ 1. Các tín hi u ñ i tho i g m: - PC4 tín hi u ra ñ ch t s li u, có th dùng PC7 ( OBFA ) thay th . - PC6 tín hi u vào cho ACK , xác nh n ñã in s li u. - PC3 dùng ñ yêu c u ng t chương trình, ñưa vào chân INTR c a VXL. Nh s d ng ch ñ 1, các tín hi u PC6, PC7 s t ñ ng thu phát mà không c n l nh c a chương trình, tr PC4 ph i ñưa l nh. V i vi c n i vào INTR c a VXL, chương trình ph c v ng t không c n l nh ki m tra tr ng thái c a PC6. 8255 PA0 ÷ PA7 Máy PC5 Data strobe in Reset Reset Busy PC1 D0 ÷ D7 D0 ÷ D7 RD RD VXL WR WR A0 A0 PC0 Busy Máy A1 A1 PC4 ñ c A2 ÷ A19 Gi i driver right CS PB0 ÷ PB7 băng mã ñ a ch Hình 2.9: Ví d GN 8255 ch ñ 0. Gi ng viên: Nguy n Văn Minh Trí 37

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi D0 ÷ D7 D0 ÷ D7 PA0 ÷ PA7 PC4 Data strobe VXL INTR INTRA PC6 PC3 ACK INTA PC7 OBFA Máy in 8255 Hình 2.10: Ví d GN 8255 ch ñ 1. 8255 PA0 ÷ PA7 D0 ÷ D7 DAC Reset Reset L i ra PB0 Ch t s li u tương t D0 ÷ D7 D0 ÷ D7 PB1 Cho phép ñưa ra RD RD VXL WR WR ADC A0 A0 PB2 Cho phép trích m u L i vào A1 A1 Ch t s li u tương t PB3 A2 ÷ A19 Gi i CS D0 ÷ D7 mã ñ a ch Hình 2.11: Ví d GN 8255 ch ñ k t h p. Hình 2.11 mô t ví d ghép n i 8255A ch ñ 2 c a c a PA và ch ñ 0 c a c a PB. . 2.3.4 L p trình cho 8255A Vi m ch c ng song song l p trình ñư c PPI 8255 có kh năng ho t ñ ng trong các ch ñ ho t ñ ng khác nhau các ch ñ ho t ñ ng này có th k t h p ñư c v i nhau t o kh năng l p trình ñi u khi n ho t ñ ng m t cách linh ho t. Khi vi t chương trình cho 8255A ho t ñ ng, ta ph i : - Vi t lưu ñ thu t toán. - Xác ñ nh t ñi u khi n ch ñ cho thanh ghi ñi u khi n, t tr ng thái cho t ng m ch c th . - Chương trình kh i phát b ng l nh ghi vào thanh ghi ñi u khi n. - ðưa n i dung các bít cho các c a dùng ñ ñi u khi n TBNV. - ð c và ki m tra tr ng thái : là thanh ghi tr ng thái n u 8255 dùng ch ñ 1,2; là m t c a ghi tr ng thái TBNV n u ch ñ 0. - ðưa s li u vào hay ghi s li u ra các c a. Gi ng viên: Nguy n Văn Minh Trí 38

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi Ví d vi t chương trình ñi u khi n ñưa s li u ra máy in như trên hình 2.9, và ñ a ch cao dành cho máy in xác ñ nh là 3FE18h. Lưu ñ thu t toán th hi n trên hình 2.12. B tñ u B tñ u L p xung ch t PC4 ð c tr ng thái – PC1 Yes Máy in b n? ð c tr ng thái – PC0 No Yes ðưa s li u ra Máy ñ c b n? No Xoá xung ch t PC5 ð c s li u vào L p xung ch t PC5 Xoá xung ch t PC4 K t thúc K t thúc Hình 2.12: Lưu ñ trao ñ i d li u gi a MVT và máy in, máy ñ c băng. Xác ñ nh các thanh ghi ch ñ và chi u c a c a: 3FE18h ⇒ A19 …. A3 A2 A1 A0 T b ng 1.17, ta có ñ a ch sau: PA có ñ a ch addr_A := 3FE18h PB có ñ a ch addr_B := 3FE19h PC có ñ a ch addr_C := 3FE1Ah Thanh ghi ñi u khi n addr_dk := 3FE1Bh Xác ñ nh t ñi u khi n và t tr ng thái: Không dùng ch ñ l p c nên D7=1 PA ch ñ 0, c a ra nên D6=0 D5=0 D4=0 N a c a C cao là c a ra nên D3=0 PB ch ñ 0, c a vào nên D2=0 D1=0 N a c a C th p là c a vào nên D0=1 Ta có t ñi u khi n sau: Data_dk := 81h (=1000 0001 B) T tr ng thái cho các c ng PC: PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0 Cho PC5 0 0 1 0 0 0 0 0 ⇒ data_C5 := 20h Gi ng viên: Nguy n Văn Minh Trí 39

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi Cho PC4 0 0 0 1 0 0 0 0 ⇒ data_C4 := 10h Cho PC1 0 0 0 0 0 0 1 0 ⇒ data_C1 := 02h Cho PC0 0 0 0 0 0 0 0 1 ⇒ data_C0 := 01h Chương trình vi t b ng Pascal như sau: Begin {Gán các bi n} Port[addr_dk] := data_dk; Repeat Var1 := port[addr_C]; Until ((var1 and data_C1)=data_C1); Port[addr_A] := ‘s’; Port[addr_C] :=0; Port[addr_C] := data_C5; End Gi ng viên: Nguy n Văn Minh Trí 40

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi CHƯƠNG 3: GHÉP N I TRAO ð I D LI U N I TI P 3.1 Gi i thi u chung v trao ñ i d li u n i ti p 3.1.1 Yêu c u trao ñ i d li u n i ti p Trao ñ i d li u n i ti p là trao ñ i l n lư t t ng bit, trên m t ñư ng dây duy nh t. Do ñó ít t n kém v ñư ng dây, nhưng t c ñ truy n th p. S trao ñ i này do các yêu c u: - Thi t b phát hay nh n d li u t ng bit. Ví d VXL 8085 phát t ng bit l i ra n i ti p SOD (chân s 4) và nh n d li u l i vào n i ti p SID (chân s 5); và TBNV n i ti p như máy cassette, ñĩa t , máy in n i ti p … - Kho ng cách gi a hai thi t b trao ñ i d li u là l n (có th ñ n hàng ngàn km ho c hơn), do v y vi c dùng 8 ñư ng dây truy n d li u song song là r t t n kém. Ngoài ra, ngư i ta có th dùng luôn ñư ng dây ñi n tho i ñ trao ñ i d li u, thông qua b ñi u ch - gi i ñi u ch (MODEM) ði u khi n n i ti p có 2 lo i truy n d li u: -truy n d li u ñ ng b (t c ñ nhanh). - truy n d li u không ñ ng b (t c ñ ch m). 1. Trong trao ñ i d li u ñ ng b : D li u ñư c truy n 1 l n g m 1 kh i nhi u byte, ñư c ch n ñ u và cu i b i ký t SYNC( mã ASCII là 16h). M i kh i có th hàng trăm byte hay hàng trăm Kbyte. sync sync d li u ð truy n ñi c n có s ñ ng b v t c ñ gi a máy phát và máy thu, có 2 cách ñ ñ ng b - M t máy phát xung ñ t nơi phát và truy n t i máy thu b i m t ñư ng dây khác. Do ñó t n thêm m t ñư ng dây H này s d ng 1 máy phát xung ñ ng b ñ cung c p xung ñ ng b cho c hai bên phát và thu. Phát Thu ð ng b - Máy thu ch tr ng thái ch , khi có ký t ñ ng b SYNC thì máy phát xung nh p trong máy thu b t lên và chuy n sang ch ñ thu xung ñ ng b ñư c kích ho t b i kí t SYNC. Phát Thu ð ng b Gi ng viên: Nguy n Văn Minh Trí 41

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 2. Trong trao ñ i thông tin không ñ ng b : Các byte ñư c ñ t trong m t khung và truy n ñ c l p v i nhau, g i là m t l i tin. D ng thông tin truy n như sau: D li u truy n có th 5,6 ,7,8 bit; thông thư ng là 7 bit ( n u truy n s li u và ch cái) hay 8 bit ( n u truy n c các ký t m r ng ñ ñi u khi n h t File). M t l i tin g m: - 1 bit Start thư ng là m c 0 (+12V). Theo chu n RS232C, tín hi u t máy tính qua c ng Com, m c ñi n áp là ±12 V và ñư c qui ñ nh:0=12V, 1= -12V. - 5÷8 bit d li u, ñây d li u truy n ñi là mã ASCII, như s “0” s ñư c truy n ñi là mã ASCII = 48 = 030h ch không ph i là truy n ñi “0”. - 1 bit b c dùng ñ ki m tra tính ch n l d li u truy n. T ng s bit 1 c a m t l i tin (k c bit ch n l ) s ñư c ghi vào bit ch n l và ñư c ki m tra so sánh nơi phát và nơi thu. - 1, 1.5 hay 2 bit Stop (tuỳ theo s l a ch n trư c khi trao ñ i) cũng m c 1. S bit Stop th c ch t là ñ dài c a tín hi u Stop m c logic 1. Bit Start dùng ñ ñ ng b xung nh p máy phát và máy thu. N u kho ng cách g n dư i 300m, s thu phát là không c n MODEM. nh ng kho ng cách l n ngư i ta không dùng máy phát xung ngoài mà dùng MODEM ñ t o xung ñ ng b cho c máy phát và máy thu. Vi c dùng MODEM là ñ ch ng nhi u trên ñư ng truy n. Trên ñư ng dây ñi n tho i, ngư i ta không phát t ng bit 0/1 mà dùng MODEM (modulation-demodulation) ñ ñi u ch tín hi u thành d ng xoay chi u (0÷2400 Hz, 1÷1200 Hz) và truy n tín hi u xoay chi u ñó. 3.1.2 M ch trao ñ i d li u n i ti p. 1. M ch không c n b ghép n i: -s d ng 2 chân ra-vào n i ti p SID ( serial IN) và SOD ( serial OUT) c a vi x lý 8085 ñ trao ñ i. -có th dùng 1 chân c a l i vào ra song song c a VXL ñ làm chân vào ra n i ti p. Trao ñ i tin ki u này không ph c t o trong c u t o m ch nhưng ph c t p trong quá trình l p trình và theo dõi thi t b , ñòi h i nhi u th i gian x lý. Thi t b ngoài vào/ra song song VXL SOD D SID Thanh ghi d ch CLK C Hình 3.1: M ch không c n BGN 2. M ch trao ñ i c n ghép n i song song-n i ti p: Gi ng viên: Nguy n Văn Minh Trí 42

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi BGN có ch c năng chuy n d li u song song t máy tính (h VXL) thành tín hi u d ng n i ti p và truy n ñ n TBNV. ð truy n chính xác, BGN ngoài ch c năng chuy n d li u song song thành n i ti p, nó còn t o ra các bit Start, stop, parity ñ ñóng khung d li u. Lo i này làm vi c ñơn gi n nhưng không m r ng ñư c thi t b ngo i vi, kho ng cách truy n tin ng n. BGN TBNV VXL ss-nt (VXL) nt Hình 3.2: M ch c n BGN ss-nt Trong ñó, song song là ss, n i ti p là nt. 3. M ch có KGN song song- n i ti p và n i ti p-song song: H này cũng gi ng như h trên, ch khác là TBNV làm vi c v i d li u song song, nên c n có BGN trung gian chuy n d li u song song thành n i ti p. BGN BGN TBNV VXL ss-nt nt-ss (VXL) ss Hình 3.3: M ch c n BGN ss-nt và nt-ss 4. M ch có BGN, MODEM và RS232C: RS-232C RS-232C MODEM MODEM BGN ñư ng dây BGN VXL ss-nt TBðC ñi n tho i ss-nt (VXL) ss Hình 3.4: M ch c n BGN ss-nt, RS 232 và MODEM. H này thông d ng và thư ng xuyên g p trong th c t . Trong ñó VXL thư ng là 1 máy vi tính, còn thi t b ñ u cu i (TBðC) có th là 1 ñ i tư ng b t kỳ. N u TBðC là máy vi tính thì h th ng dùng ñ trao ñ i File. Chú ý: Chu n RS232C có m c ñi n áp là ±12V. Chu n RS422 có m c ñi n áp là ±15V. Chu n RS485 có m c ñi n áp là ±30V (ñi n tho i). ð chuy n t RS232C thành RS485 hay RS422 s có nh ng b chuy n (shift) trung gian, thông thư ng ñó là nh ng b ñ m, v a t o m c tín hi u,v a ph i h p tr kháng. Gi ng viên: Nguy n Văn Minh Trí 43

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 3.1.3 Th t c trao ñ i d li u n i ti p 1. Th t c phát d li u TxD (Tranceiver Data) : • TBðC (hay MVT) g i tín hi u DTR (Data Terminal Ready) m c 0 ñ n MODEM báo hi u ñã s n sàng. • MODEM tr l i TBðC b ng tín hi u DSR (Date Set Ready) m c 0. • N u TBðC có 1 ký t s n sàng g i ñi, nó g i RTS (Request To Send) ñ n MODEM • MODEM g i tín hi u CD (Carrier Detect) cho TBðC ñ báo hi u liên l c ñã thông v i MTV. • Khi MODEM s n sàng phát s li u trên ñư ng dây, MODEM phát xung nh p và tín hi u CTS (Clear To Send) ñ n TBðC (xung nh p trên ñư ng dây). • TBðC g i các ký t s li u (SDU) cho MODEM. • Khi TBðC g i xong, nó nâng tín hi u RTS lên cao ñ báo cho modem bi t là ñã phát xong. • MODEM tr l i cho TBðC b ng tín hi u CTS m c cao, báo hi u hoàn thành vi c truy n tin. Qua ñó ta th y vi c g i ñi kí t b ng modem nhi u th t c và do ñó t c ñ ch m 2. Th t c nh n d li u RxD (Receiver Data) Trong quá trình nh n tin, ph i b o ñ m máy tính ñã s n sàng nh n ,khi ñó : • TBðC phía thu g i DTR m c th p cho MODEM báo nó ñã s n sàng (Data terminal ready) • MODEM thu g i tín hi u tr l i b ng DSR . • MODEM thu nh n tín hi u CD t ñư ng dây và kích g i tín hi u nh p MODEM cho TBðC. • TBðC phát tín hi u RTS cho modem (Request to Send). • MODEM g i tín hi u CTS m c th p cho TBðC (Clear to Send) ñ báo MODEM s n sàng nh n tin. • MODEM nh n TxD trên ñư ng dây, sau ñó ph i ñi u ch thành các bit 0/1 và l n lư t g i chu i tín hi u RxD cho TBðC. • Khi thu xong, TBðC nâng tín hi u RTS lên cao, báo cho MODEM là ñã thu xong • MODEM tr l i b ng nâng tín hi u CTS lên cao, ñ báo quá trình nh n ñã xong. Vi c ti n hành chuy n d li u ss/nt hay nt/ss ñư c th c hi n b i các thanh ghi d ch (Shift register). Các thanh ghi này có tác d ng khi nh n 1 byte song song ñ u vào nó s cho ñ u ra m t chu i bit k ti p nhau theo th t t bit th p ñ n bit cao c a byte. ð i v i máy tính, các ch c năng trên ñư c th c hi n thông qua vi m ch 8251 c a hãng INTEL. Gi ng viên: Nguy n Văn Minh Trí 44

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 3.2 M ch thu phát di b v n năng UART 8250 M ch URAT 8250 (Universal Asynchronous Receiver/Transmitter) ñư c l p ráp trong các máy IBM XT, là m t IC thu phát không ñ ng b có th l p trình ñư c, nó th c hi n ch c năng giao ti p gi a máy tính và TBNV. Trong các máy PC/AT hi n nay s d ng UART 16450 còn trong PS/2 và các AT ñ i m i l i dùng UART 16550 vì 8250 và 16450 không ñ t ñ n t c ñ 115200 baud ñư c. Th c ra t c ñ này ng d ng t t trong k thu t truy n tin trên m ng, còn trong các thi t b công nghi p TBNV nói chung, thư ng ch c n t i ña 19200 baud là ñư c, thông d ng là 9600 baud. 3.2.1 Sơ ñ kh i và ch c năng các kh i c a UART 8250 1. Mô t vi m ch: Vi m ch 8250 có 40 chân như trên hình v : Hình 3.5: Sơ ñ chân 8250 Ch c năng các chân g m: - Các chân t 1- 8 (D0- D7 ): Các chân d li u, 8 chân này ñư c n i v i bus d li u. Qua 8 chân d li u này mà d li u ñư c ñi t bus t i dư i d ng song song sau khi qua vi m ch 8250 bi n ñ i thành tu n t ñ ñi t i c ng RS232. D li u t c ng RS232 t i dư i d ng tu n t , sau khi ñi qua vi m ch 8250 ñư c bi n ñ i thành song song và qua 8 chân này truy n lên bus. - Chân s 9 (RCLK ): nh n xung ñ ng h ñưa ra t b t o t c ñ . - Chân s 10 (SIN): nh n d li u tu n t ñi t i t c ng RS232. - Chân s 11 (SOUT): G i d li u tu n t sang c ng RS232. - Chân s 12,13,14 (CS0 -CS2): Chip select - tín hi u ch n vi m ch. - Chân s 15 ( BOUDOUT ) : L i ra c a b t o t c ñ . - Chân s 16,17 (XTAL1,XTAL2) :L y xung Clock t b phát nh p b ng th ch anh t i v i t n s 3,072 MHz. - Chân 18(DOSTR ): I/O write. - Chân s 19 ( DOSTR ) : Ð o c a I/O write - Chân s 20 (Vss ): n i ñ t Gi ng viên: Nguy n Văn Minh Trí 45

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi - Chân s 21 (DISTR) : I/O Read . - Chân s 22 ( DISTR ): Ð o c a I/O Read . - Chân s 26,27,28 ( A0 - A2 ): nh n ñ a ch truy n t i ñ gi i mã l nh . - Chân s 30 (INTRPT) : Interrupt Control Logic . - Chân s 32 ( RTS ) : Request To Send ( yêu c u g i ) . - Chân s 33 ( DTR ) : Data Terminal Ready .(D li u s n sàng ) - Chân s 35 (MR) : Reset . - Chân s 36 ( CTS ) : Clear To Send - Chân s 37 ( DSR ) : Data Set Ready . - Chân s 38 ( DCD ) : Data Carrier Detect . - Chân s 39 ( RI ): Ring Indicate . - Chân s 40 (VDo) : n i v i ngu n m t chi u +5V. (3F8) (3FB) (3F8) (3F9) (3FD) (3F8) (3FC) (3FE) (3F9) (3FA) Hình 3.6: Sơ ñ kh i 8250 Như v y, 8250 có 11 thanh ghi n i, v i cách truy c p như b ng sau: B ng 3.1: ð a ch các thanh ghi c a 8085 DLAB A2 A1 A0 ð c/ghi Thanh ghi Gi ng viên: Nguy n Văn Minh Trí 46

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 0 0 0 0 ñ m thu (RBR) và ñ m phát (THR) 0 0 0 1 ð c/ghi cho phép yêu c u ng t (IER) 1 0 0 0 ð c/ghi ch t chia ph n th p (LSB) 1 0 0 1 ð c/ghi ch t chia ph n cao (MSB) x 0 1 0 ð c nh n d ng ng t (IIR) x 0 1 1 ð c/ghi ñi u khi n dòng (LCR) x 1 0 0 ð c/ghi ñi u khi n MODEM (MC) x 1 0 1 ð c/ghi tr ng thái dòng (LSR) x 1 1 0 ð c/ghi tr ng thái modem (MSR) x 1 1 1 ð c/ghi nh nháp (DM) M i thanh ghi trong 8250 tương ng v i m t ñ a ch c ng, trong ñó có hai thang ghi ñ c bi t, nó có ch c năng có th thay th tuỳ thu c giá tr bit DLAB (divitor latch access bit –Bit truy c p ch t) (DLAB là bit D7 c a thanh ghi d ng s li u). • N u DLAB = 1 thì thanh ghi th c hi n ch c năng ch t chia ph n cao và ph n th p. • n u DLAB = 0 , hai thanh ghi dùng ñ ñ m và nh n d li u, và IER. 2. Mô t các thanh ghi: a) Thanh ghi ñ m thu (Receiver Buffer Register – RBR) ng v i DLAB = 0, thanh ghi có ñ a ch là 3F8h (COM1), hay 2F8h (COM2): Khi 8250 nh n ñư c ký t qua chân SIN (chân 10) ký t ñư c chuy n vào thanh ghi d ch, t i ñây nó ñư c tháo khung (các bit start, stop, parity) và n p song song vào thanh ñ m thu (lưu ý thanh ghi có 8 bit). CPU ch ñ c d li u trong thanh ghi này vì nó thao tác v i BUS d li u song song t i thi u m i l n là 1 byte. b) Thanh ghi ñ m phát (Transmitter Holding Register – THR) tương ng v i DLAB = 0, ñ a ch là 3F8h (2F8h) Ký t c n phát ñi ph i ñư c ghi t thanh ghi vào, thanh ghi này nó n m ch (holding) ñó cho ñ n khi ký t trư c nó ñư c phát ñi, sau ñó nó ñưa vào thanh ghi d ch c a b phát, t i ñây nó ñư c ñóng khung và ñưa ra t ng bit m t vào chân SOUT (chân 11) c a 8250, d li u ñ u ra ñây có d ng n i ti p. c) Thanh ghi cho phép ng t (Interrupt Enable Register - IER), bit DLAB = 0 , ñ a ch 3F9h (COM1) hay 2F9h (COM2) Thanh ghi này th c hi n ñ cho phép/c m các nguyên nhân gây ra ng t khác nhau. Trong khi 8250 ho t ñ ng, có tác ñ ng ñ n CPU thông qua chân INTRPT (chân 30), m i bit trong các bit D3, D2, D1, D0 m c cao s cho phép các ho t ñ ng tương ng v i các bit ñ ñưa ra nguyên nhân ng t tương ng, và c m ng t khi ghi 0 vào các bit. Bit Ch c năng 7-4 D tr , luôn ñ t b ng 0. 3 cho phép 8250 phát yêu c u ng t tr ng thái MODEM Gi ng viên: Nguy n Văn Minh Trí 47

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi 2 cho phép 8250 phát yêu c u ng t theo tr ng thái d ng truy n nh n ho c ng t dòng thông tin (l i ch n l , tràn khung). 1 cho phép 8250 phát yêu c u ng t khi thanh ghi ñ m phát r ng. 0 cho phép 8250 phát yêu c u ng t khi thanh ghi ñ m thu ñ y, d li u ñã s n sàng d) Thanh ghi ch t chia ph n th p (Divisor Latch - LS) tương ng DLAB = 1, ñ a ch là 3F8h, hay 2F8h. e) Thanh ghi ch t chia ph n cao (Divisor Latch – MS) tương ng DLAB = 1, ñ a ch là 3F9h, hay 2F9h. ð ñ t t c ñ truy n mong mu n, giá tr tính toán ñư c ñ t trong hai thanh ghi, ñư c g i là thanh ghi ch t chia t c ñ ñư c tính theo công th c T n s nh p chu n B chia = 16 x t c ñ baud mong mu n - t n s nh p chu n do ñ ng h th ch anh c a 8250 phát ra, nó b ng 1,8432 MHZ - t c ñ t i ña tính toán là 115200 baud. - t c ñ baud ñ th c hi n các chân SIN, SOUT. B ng ch m i liên h gi a t c ñ s li u và các h s chia d ng hexa decimal như sau: Baud S chia Baud S chia 50 0900 1200 0060 110 0417 2400 0030 150 0300 4800 0018 300 0180 9600 000C 600 00C0 11520 0001 Qua ñó ta th y giá tr trong thanh ch t chia c n 1 byte rư i ñ lưu t t c . ð thu n ti n, ngư i ta s dùng 2 byte và ghi vào 2 thanh ghi, ñó chính là LSB và MSB. f) Thanh ghi nh n d ng ng t (Interrupt Identification Register - IIR), ñ a ch là 3FAh, hay 2FAh. Thanh ghi nh n d ng ng t (ch có th ñ c) ch a mã m c ưu tiên cao nh t c a các yêu c u ng t (t i chân 30-INPUT c a 8250) ñang ch ñư c ph c v . N u có nhi u ng t cùng m t lúc thì IIR s ch a mã ng t nào c n x lý trư c. Do v y khi c n x lý ng t, CPU c n ñ c bit D0 c a thanh ghi này ñ bi t có yêu c u ng t và ki m tra các bit D1 và D2 ñ xác ñ nh ngu n g c các yêu c u ng t. Sau khi 8250 b Reset, ch có yêu c u ng t ưu tiên s m t ñư c ph c v . Ta có th thay ñ i Gi ng viên: Nguy n Văn Minh Trí 48

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi ñi u này b ng cách dùng m t n che ñi các bit yêu c u ng t nào ñó b ng cách ghi vào thanh ghi IIR các giá tr bit thích h p. Các bit D7÷D3 luôn ñ t b ng 0. D2, D1: mã hoá các yêu c u ng t có m c ưu tiên cao nh t ñang ch ph c v . D2 D1 M c ưu tiên Nh n di n ng t 0 0 4 Tr ng thái MODEM ⇒ chương trình ñ c tr ng thái MODEM 0 1 3 Thanh ghi ñ m phát r ng 1 0 2 TG ñ m thu ñ y, s li u ñã s n sàng 1 1 1 tr ng thái dòng ñã thay ñ i D0=0: có yêu c u ng t D0=1: không có yêu c u ng t T các nh n d ng ng t trên, VXL s chuy n ñ n các ñ a ch ch a các chương trình con ph c v ng t. VXL s xoá các bit D0, D1, D2 v 0 sau các thao tác: -ñ c thanh ghi tr ng thái chu i. -ñ c d li u t thanh ghi ñ m thu. -ghi vào b phát ho c ñ c thanh ghi nh n di n ng t. -ñ c tr ng thái thanh ghi thao tác MODEM (RS232-C). g) Thanh ghi ñi u khi n dòng (Line Control Register – LCR), ñ a ch là 3FBh, hay 2FBh. Thanh ghi này còn có tên là thanh ghi ñ nh khuôn d ng d li u vì nó quy t ñ nh khuôn d ng c a d li u truy n trên ñư ng dây. Bit Ch c năng 7 =1 truy nh p thanh ghi ch t chia (LSB & MSB) ñ l p t c ñ baud =0 truy nh p IER,THR,RBR 6 ð t cho phép tín hi u Break 5-3 B5 B4 B3 Ch n ch n l x x 0 Non 0 0 1 Odd 0 1 0 Even 1 0 1 High Parity 1 1 1 Low Parity 2 = 1 thì dùng 1.5 bit Stop n u ñ dài t là 5, còn n u ñ dài t 6-8 bit thì có 2 bit Stop. = 0 thì dùng 1 bit Stop 1-0 B1 B0 S bit data 0 0 5 0 1 6 1 0 7 1 1 8 Gi ng viên: Nguy n Văn Minh Trí 49

- Tài li u môn h c: Ghép n i và ñi u khi n thi t b ngo i vi ð hi u tín hi u Break, ta xem ví d khung d li u trên v i 8 bit data, không ki m tra ch n l và 1 bit Stop. Khi ñư ng dây tr ng thái Mark, m c logic là 1. Bit Start s là m c logic 0. Sau ñó t ng bit data s ñư c g i trên ñư ng dây. Bit Stop (logic 1) sau ñó ñư c gán vào ñ k t thúc vi c truy n. Sau bit Stop s là bit logic 0, có nghĩa là bit Start c a m t d li u m i. N u không có thêm d li u truy n ñi, ñư ng dây ph i tr ng thái r i, m c logic 1. Do ñó n u ñư ng dây gi tr ng thái 0 sau bit Stop trong m t th i gian b ng ñ dài 1 t , tín hi u Break s ñư c t o ra. Tín hi u Break là tín hi u báo cho CPU hay MODEM bi t ký t truy n ñã xong và ñang t m ng t vi c truy n. h) Thanh ghi ñi u khi n MODEM (MODEM Control Register – MCR), ñ a ch 3FCh Thanh ghi này còn g i là thanh ghi ñi u khi n các tín hi u ra c a MODEM vì nó cho phép ñi u khi n các tín hi u t i các chân DTR (chân 33) và DTS (chân 32) c a 8250. Bit Ch c năng 7-5 D tr , luôn ñư c thi t l p v 0. 4 =1 cho phép 8250 làm vi c ch ñ n i vòng c c b ñ ki m tra các ch c năng c a 8250. =0 làm vi c ch ñ thư ng. 3 =1 : kích ho t k t xu t OUT2 2 =1 : kích ho t k t xu t OUT1 1 =1 : tín hi u t i chân RTS c a 8250 ñư c chuy n v m c 0, máy tính phát chuy n tín hi u RTS t i MODEM ñ báo hi u nó ñã s n sàng phát d li u. 0 =1 : tín hi u t i chân DTR c a 8250 ñ t m c 0, lúc này máy tính g i tín hi u DTR t i MODEM (hay t i MVT ñ u kia n u giao ti p không dùng MODEM) ñ báo hi u nó s n sàng làm vi c (tín hi u g i t i chân s 4 c a DB9 hay chân 20 c a DB25). i) Thanh ghi tr ng thái dòng (Line Status Register – LSR) ñ a ch 3FDh Ch c năng thanh ghi này cho bi t tr ng thái dòng tín hi u trên ñư ng dây như th nào, các bit D0÷D5 ñ u có th gây ra ng t n u các bit tương ng trong thanh ghi IER ñư c l p . Các bit tr ng thái có ý nghĩa như sau: Bit Ch c năng Gi ng viên: Nguy n Văn Minh Trí 50

CÓ THỂ BẠN MUỐN DOWNLOAD

-

Nghiên cứu đáp ứng quá độ mạch điều khiển tốc độ của mô tơ thủy lực ROCKFORD ILLINOI S16Z3 khi ứng dụng bộ chuyển đổi số LAB- PC+ và Van servo BD90

6 p |

6 p |  860

|

860

|  229

229

-

NGHIÊN CỨU THIẾT KẾ, CHẾ TẠO MÁY BÁN NƯỚC GIẢI KHÁT TỰ ĐỘNG BẰNG KỸ THUẬT VI ĐIỀU KHIỂN

5 p |

5 p |  479

|

479

|  133

133

-

Các phương pháp và sơ đồ ghép nối vi xử lý - máy tính để điều khiển động cơ điện một chiều

15 p |

15 p |  265

|

265

|  119

119

-

Chương 2: Các phương pháp và sơ đồ ghép nối vi xử lý - máy tính để điều khiển động cơ điện một chiều

15 p |

15 p |  260

|

260

|  110

110

-

HỆ THỐNG ĐIỀU KHỂN PHÂN TÁN - CHƯƠNG 2

7 p |

7 p |  245

|

245

|  95

95

-

Phòng thí nghiệm Vi xử lý Bài thí nghiệm Vi xử lý BÀI 03: ĐIỀU KHIỂN MA TRẬN

11 p |

11 p |  250

|

250

|  65

65

-

Bài giảng Vi xử lý và lập trình hợp ngữ - Phạm Đức Long

152 p |

152 p |  198

|

198

|  56

56

-

Thiết bị ngoại vi và ghép nối . chương 2

18 p |

18 p |  110

|

110

|  35

35

-

ÔN TẬP THIẾT BỊ NGOẠI VI

67 p |

67 p |  136

|

136

|  34

34

-

Thiết kế hệ thống điều khiển số sử dụng vi điều khiển và máy tính - Chương 5

6 p |

6 p |  136

|

136

|  29

29

-

Đo và điều khiển tốc độ đo lường cơ điện một chiều

13 p |

13 p |  103

|

103

|  21

21

-

Bài giảng Điện tử máy tính - ĐH Công nghiệp Hà Nội

101 p |

101 p |  111

|

111

|  18

18

-

Giới thiệu chung về vi điều khiển - Nguyễn Quốc Cường

13 p |

13 p |  169

|

169

|  17

17

-

Chương 1 :Kiến trúc hệ VXL – MT

46 p |

46 p |  98

|

98

|  13

13

-

Đồ án Thiết kế khoan bán tự động

31 p |

31 p |  102

|

102

|  6

6

-

Jumo Imago 500: Bộ điều khiển quá trình và chương trình

88 p |

88 p |  68

|

68

|  5

5

-

Bài giảng Vi xử lý - Vi điều khiển: Chương 5.4 - ThS. Phan Đình Duy

34 p |

34 p |  71

|

71

|  5

5

Chịu trách nhiệm nội dung:

Nguyễn Công Hà - Giám đốc Công ty TNHH TÀI LIỆU TRỰC TUYẾN VI NA

LIÊN HỆ

Địa chỉ: P402, 54A Nơ Trang Long, Phường 14, Q.Bình Thạnh, TP.HCM

Hotline: 093 303 0098

Email: support@tailieu.vn