K

K

thu

thu

t

tVi

Vi x

x

lý

lý

oa

oa

ư

ư

!o

!o

"

"#

#

$

$"

"

%

%&

&

'

' (o

(o

)

)#

#

*

*a

a

+,-./

+,-./

0

0 (o

(o

)

)#

#

*

*a

a

+1-2/

+1-2/

u4

u4

5

5

*

*a

a

6

6 7

7

!8

!8 9:99

9:99

;

;

o

o

<

<

<

<"

"#

#

$

$

M

M

c tiêu v

c tiêu và

àbi

bi

n ph

n phá

áp thi

p thi

t k

t k

=

=>

>+

+5

5

+

+

$

$,-./

,-./ 6

6

1-2/

1-2/

6

6$

$

u4

u4

5

54aoo7

4aoo7?

?yAa

yAa

7u)

7u)#

#

B

B

+

+

$

$"

"C

C

D

DE

E 6

6 7

7

!8Auy

!8AuyF

F+

+

G

G

HI.

HI.

J

J

K

KE

E#

#

+

+

$

$o

o

)

)#

#

6

6 7

7

!8

!8

Auy

AuyF

F+"

+"#

#

$

$

L

LM

M

E

E#

#E

E

?

?EN)

EN)C

Ca

aJ

J"

"#

#

$

$%

%O

O

+

+

?

?ENo

ENoP

P

G

G

!o

!o o

oP

P

<

<

Q

Q+

+?

?a

a

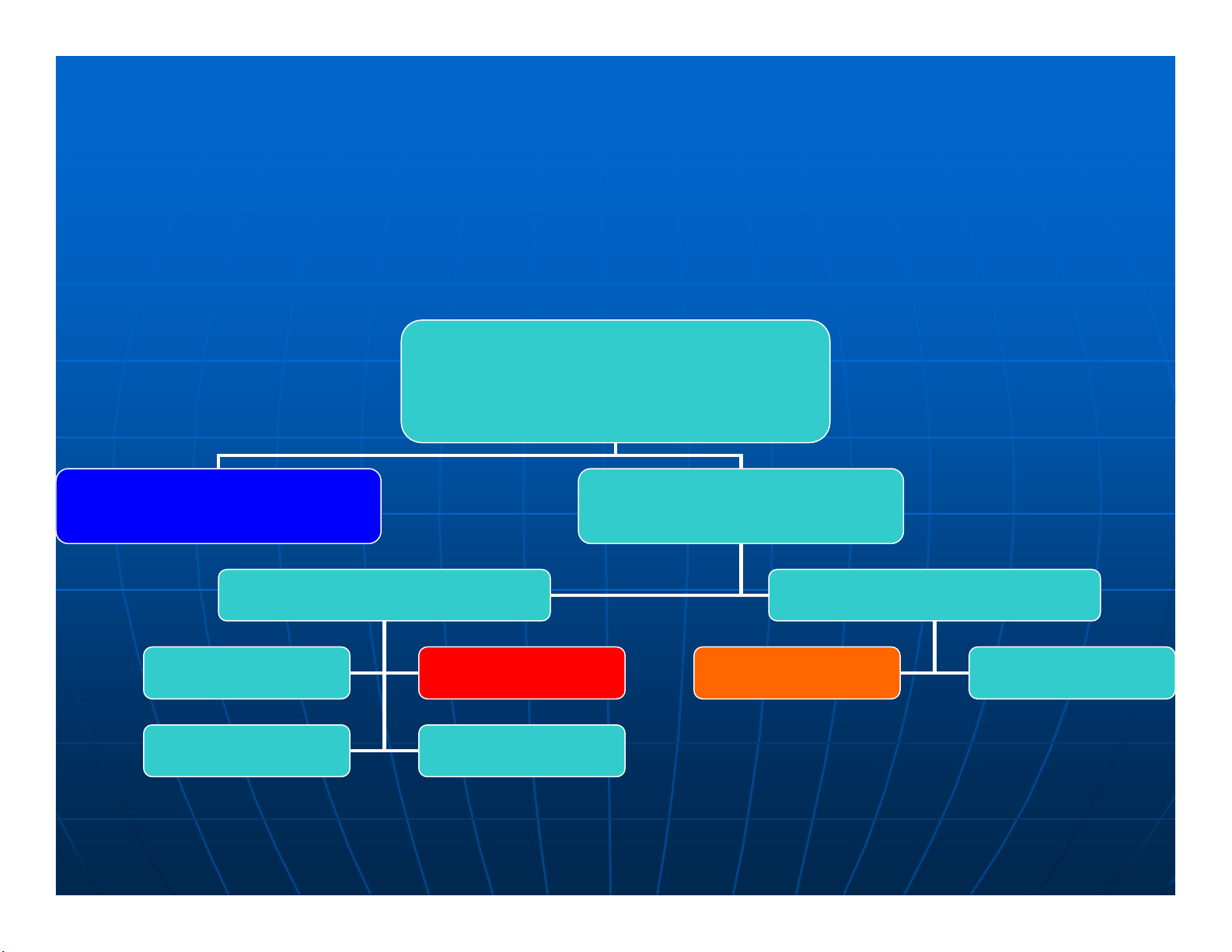

4.1

4.1 Phân lo

Phân lo

i b

i b

nh

nh

b

bá

án d

n d

n

n

Bnhbán dn

(

Semiconductor memory

)

SAM

(Sequential Access Memory)

RAM

(Random Access Memory)

ROM (Read Only Memory)RWM (Read Write memory)

PROM EPROM

EEPROM Flash ROM

SRAM DRAM

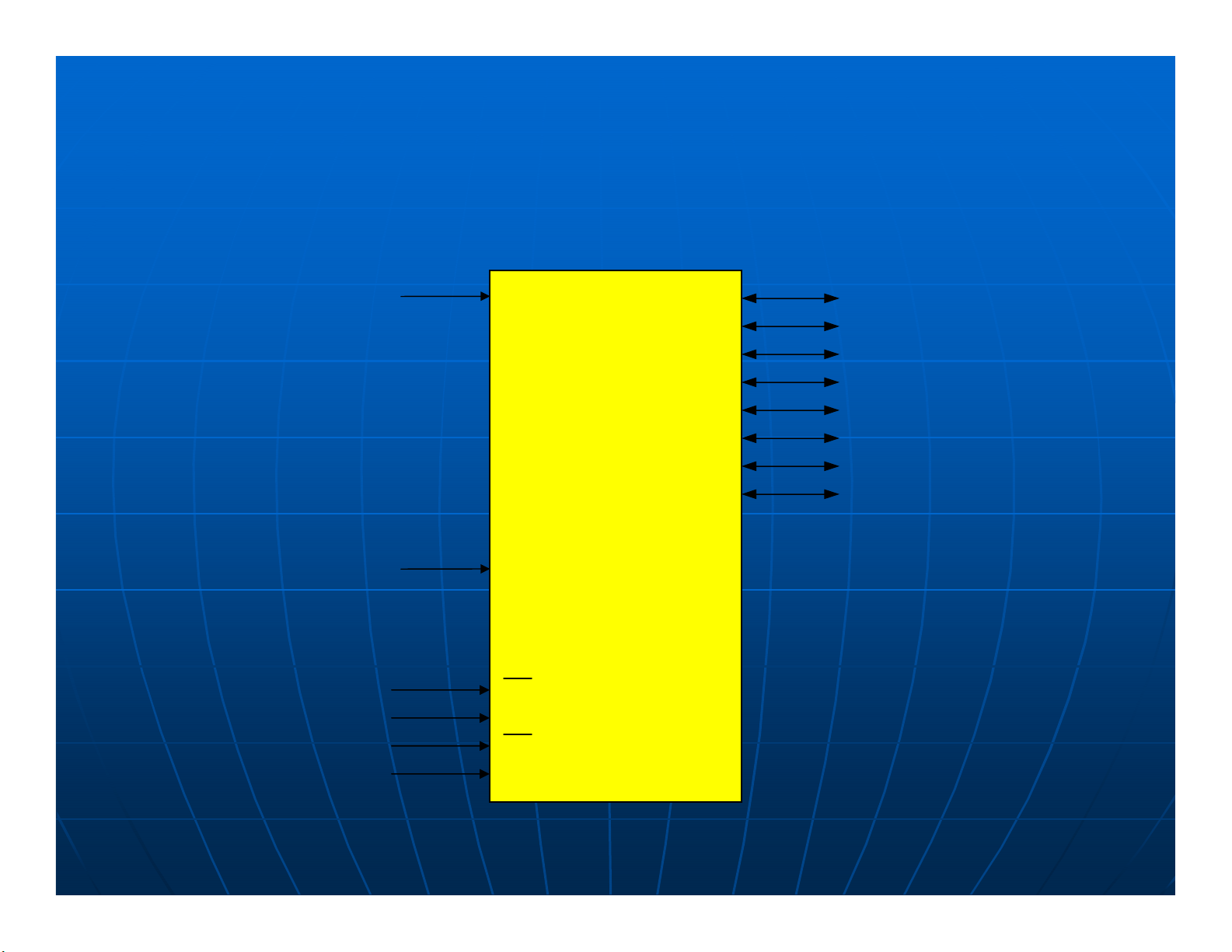

4.2

4.2 C

Cá

ác

cchip EPROM

chip EPROM

,-./

A0

A1

A2

A3

A4

A5

A6

A7

A8

Ap-1

Vpp

D0

D1

D2

D3

D4

D5

D6

D

m-1

CE

OE

PGM

+ )CaJ

)RuS

E %T !u

RuS)

+

![Giáo trình AutoCAD Pro Design: Phần 2 - Dương Đức Cảnh [Full]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20221214/phuongnguyen0520/135x160/1030337256.jpg)

![Giáo trình AutoCAD Pro Design: Phần 1 - Dương Đức Cảnh [Hướng dẫn chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20221214/phuongnguyen0520/135x160/1724121258.jpg)

![Giáo trình Autocad Trường Cao đẳng Nghề An Giang [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20220815/viastonmartin/135x160/627247906.jpg)