Giáo trình thí nghiệm vi điều khiển ứng dụng

1

BÀI 1 : XUẤT NHẬP I/O PORT:

I.MỤC ĐÍCH THÍ NGHIỆM :

Kiến thức sinh viên cần đạt được sau khi thực tập:

Liệt kê các thanh ghi liên quan đến việc xử lý tính hiệu số ở các chân vi điều khiển .

Khởi tạo các chân của vi điều khiển là ngõ ra , vào số .

Giải thích được công dụng của hàm _delay(n) , cách dùng hàm delay để chống dội cho

nút nhấn.

Lập trình điều khiển led theo yêu cầu .

Giải thích ưu khuyết điểm của ngắt .

II.DỤNG CỤ THÍ NGHIỆM :

Kít thí nghiệm + cáp USB.

Máy tính .

Nguồn 12V/1A.

III.CƠ SỞ LÝ THUYẾT :

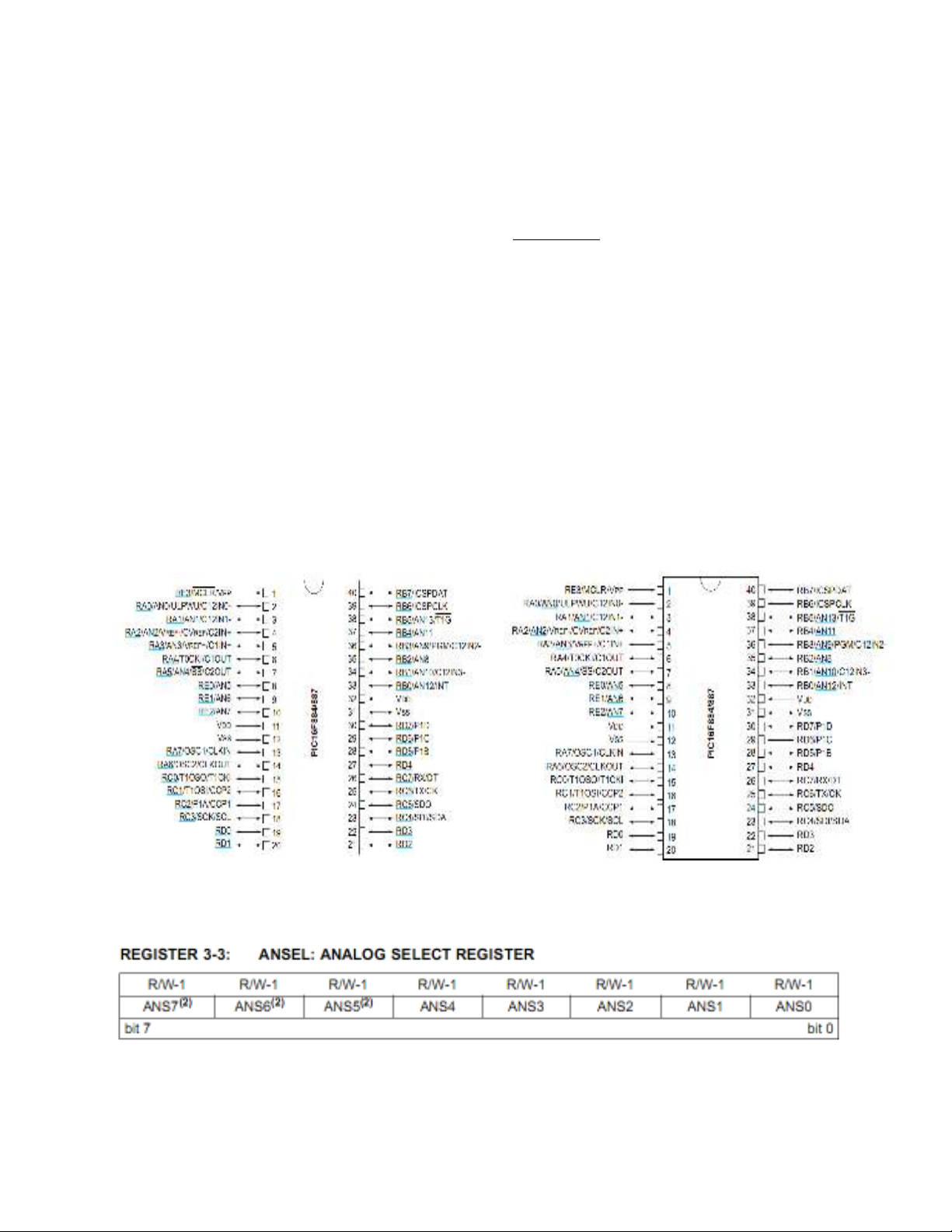

1.Thanh ghi qui định tín hiệu xử lý ở chân vi điều khiển là tín hiệu số hay tín hiệu tương

tự:

Những chân có kí hiệu ANX là những chân vừa có thể xử lý tín hiệu số vừa có thể xử lý tín

hiệu tương tự . Do đó khi làm việc với những chân này ta cần chú ý đến hai thanh ghi :

Giáo trình thí nghiệm vi điều khiển ứng dụng

2

Hai thanh ghi này có tổng cộng 14bit từ ANS0 đến ANS13 , sẽ quy định tín hiệu làm việc

của các chân từ AN0 đến AN13 là tín hiệu số hay tín hiệu analog .

ANSX=0 : Cho phép chân ANX xử lý tín hiệu số .

ANSX=1 : Cho phép chân ANX xử lý tín hiệu tương tự .

Trong đó : X= 0 – 13

2.Chức năng của thanh ghi TRIS :

Trong các chân xử lý tín hiệu số , hoạt động của chân có thể là ngõ ra (làm cho led chớp tắt,

kích transistor , điều khiển hoạt động IC....) , hay có thể là ngõ vào (đọc trạng thái nút nhấn , đọc

encoder , đọc tín hiệu từ cảm biến số....). Như vậy , để khởi tạo cho các chân là ngõ ra hay ngõ

vào tín hiệu số , chúng ta cần chú ý đến thanh ghi TRISX (X=A,B,C,D,E):

TRISXY=0:Quy định bit thứ Y của PORTX là ngõ ra (0 = Output)

TRISXY=1:Quy định bit thứ Y của PORTX là ngõ vào (1=Input)

(Trong đó :X=A,B,C,D,E ; Y=0-7)

Chú ý : PORTE chỉ có 4 bit thấp : TRISE0, TRISE1, TRISE2 ,TRISE3.

3. Chức năng của thanh ghi PORT :

Trong trường hợp xử lý tín hiệu số và là ngõ ra , thì có thể là ngõ ra mức cao (điện áp ở chân

đó là VH) , hay ngõ ra là mức thấp (điện áp là VL) sẽ do bit RXY của thanh ghi PORTX quy

định .

RXY=0 : Quy định chân thứ Y của PORTX là mức thấp(VL).

RXY=1: Quy định chân thứ Y của PORTX là mức cao(VH).

(Trong đó : X=A,B,C,D,E ; Y=0-7)

Giáo trình thí nghiệm vi điều khiển ứng dụng

3

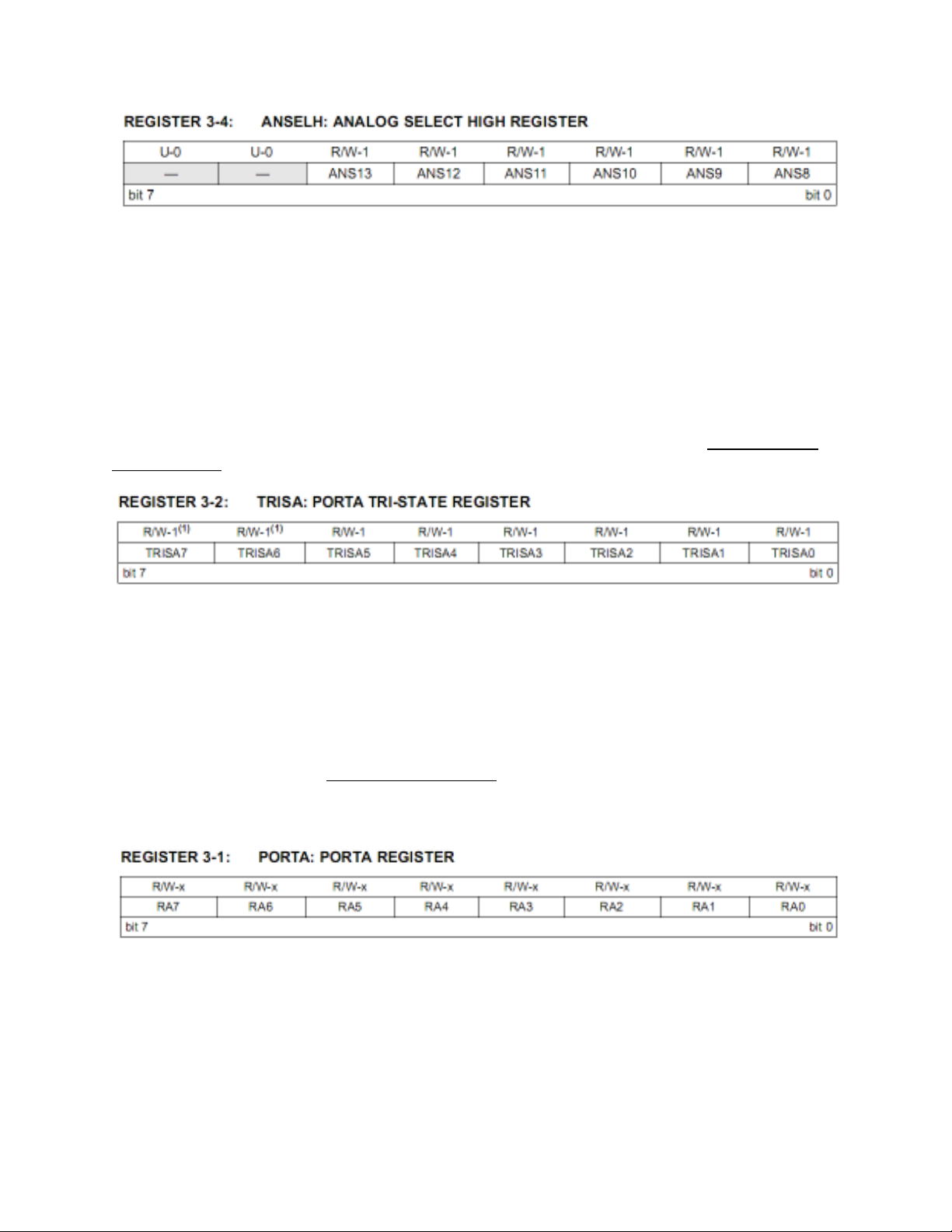

Tóm lại ta có bảng tóm tắt sau :

ANSX

TRISXY

RXY

Kết quả

0

0

0

Ngõ ra mức thấp(0V)

0

0

1

Ngõ ra mức cao(+5V)

0

1

0

Tổng trở cao (R=∞)

0

1

1

Ngõ vào , tác động mức thấp

1

x

x

Xử lý tín hiệu tương tự .

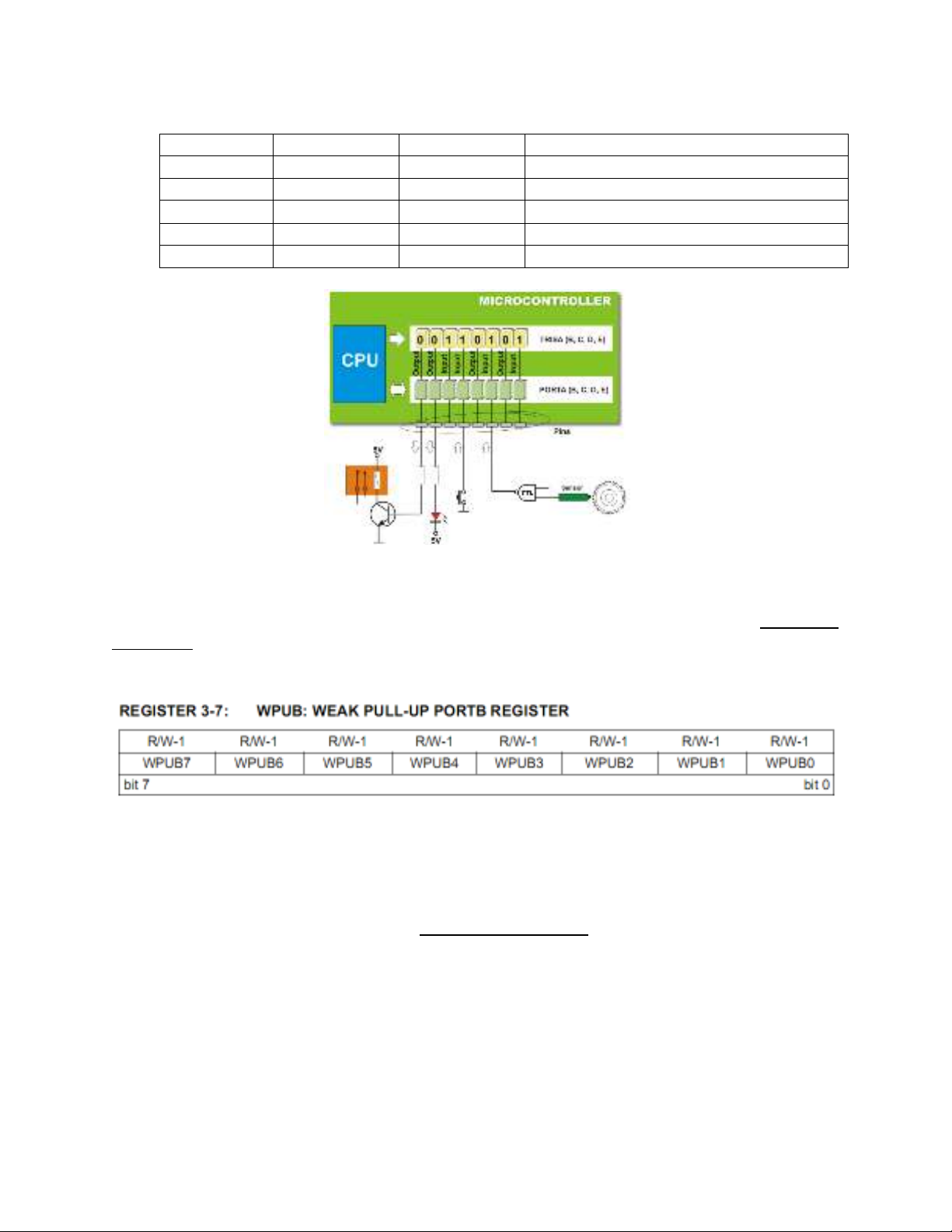

4.Những thanh ghi đặc biệt chỉ có riêng ở PORTB:

4.1.Thanh ghi hỗ trợ điện trở treo bên trong:

Để tránh trạng thái thả nổi (tín hiệu điện áp ở chân đó không rõ ràng) khi khởi tạo PORTB là

ngõ vào số , PIC16f887 tích hợp thêm vào cho PORTB các điện trở kéo lên (pull-up), để sử dụng

các điện trở này ta chú ý đến thanh ghi :

WPUBy=0: Không cho phép điện trở kéo lên ở chân thứ y của PORTB.

WPUBy=1: Cho phép điện trở kéo lên ở chân thứ y của PORTB.

Khi sử dụng điện trở kéo lên ngoài việc sử dụng thanh ghi WPUB còn phải khởi tạo bit:

RBPU

Điện trở kéo lên nên khởi tạo khi PORTB là ngõ vào số , các PORT khác không có hỗ

trợ điện trở treo trong , do đó nếu có nhu cầu sử dụng ta có thể mắc thêm điện trở bên

ngoài.

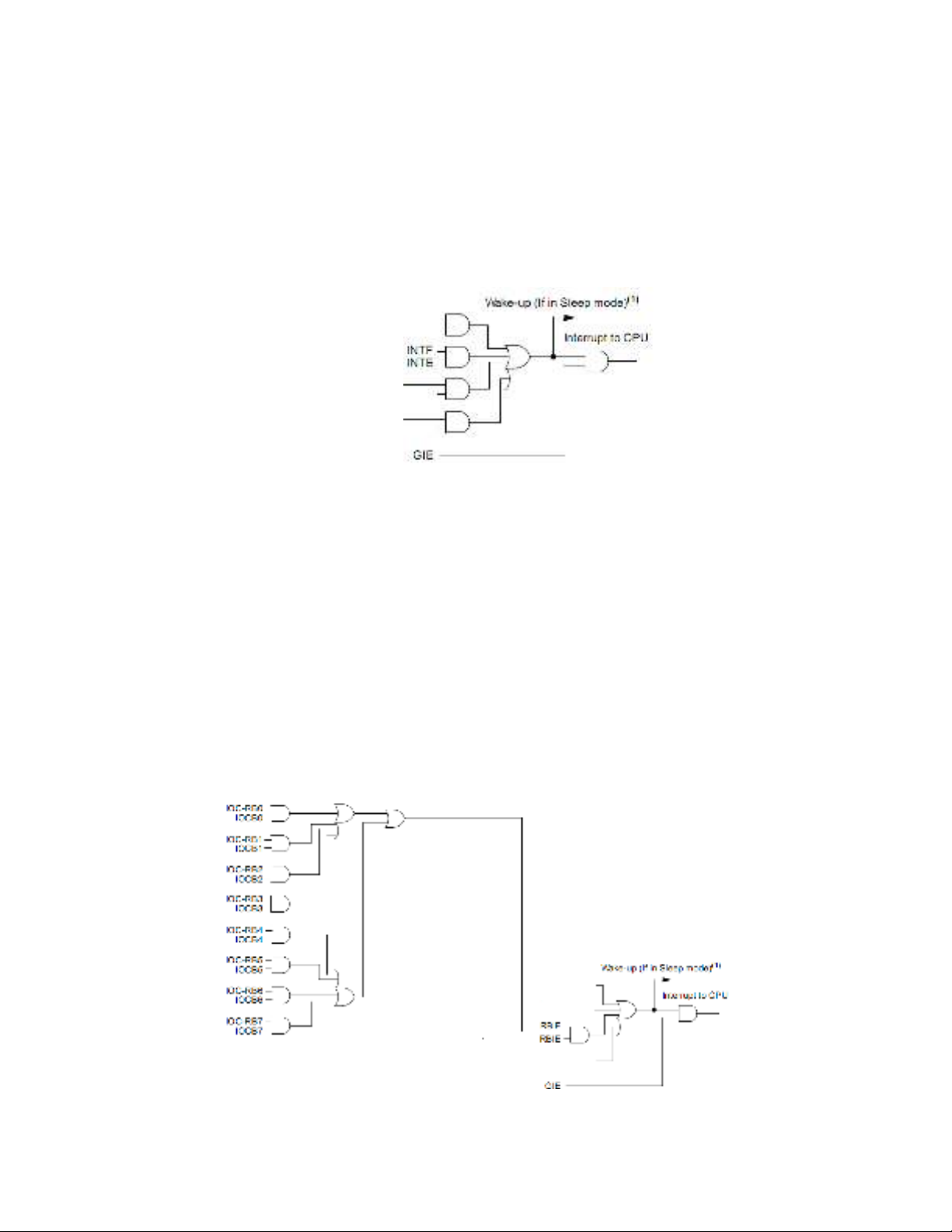

4.2.Ngắt ngoài ở chân RB0:

Để xử lý được các tín hiệu tác động tức thời , chân RB0 có hỗ trợ xử lý ngắt (interrupt ) kí

hiệu ở chân là INT, khởi tạo ngắt ngoài ở chân RB0 ta cần chú ý đến các bit sau :

INTE(Interrupt enable ) : bit cho phép ngắt ở PORTB

Giáo trình thí nghiệm vi điều khiển ứng dụng

4

INTF(Interrupt flag): cờ ngắt , bit này tự động bằng 1 khi có sự kiện ngắt (cạnh lên hay

cạnh xuống) xảy ra ở chân RB0, ta phải xóa bít này trong khi lập trình .

GIE(Global interrupt ) : bit cho phép ngắt toàn cục.

INTEDG (interrupt edge select bit ) : Bit chọn cạnh tác động để sinh ra sự kiện ngắt ở

PORTB.

INTEDG=1: Xảy ra ngắt khi có tín hiệu cạnh lên ở PORTB

INTEDG=0: Xảy ra ngắt khi có tín hiệu cạnh xuống ở PORTB

Các bước khởi tạo ngắt INT:

Bước 1 : Khởi tạo chân RB0 là ngõ vào số , điện trở treo.

Bước 2 : Khởi tạo ngắt INT

INTE=1; //Cho phép ngắt hoạt động

INTF=0; //Xóa cờ ngắt thì ngắt lần tiếp theo mới có thể xảy ra.

INTEDG=....; //Chọn cạnh tác động ngắt.

GIE=1; //Cho phép ngắt toàn cục .

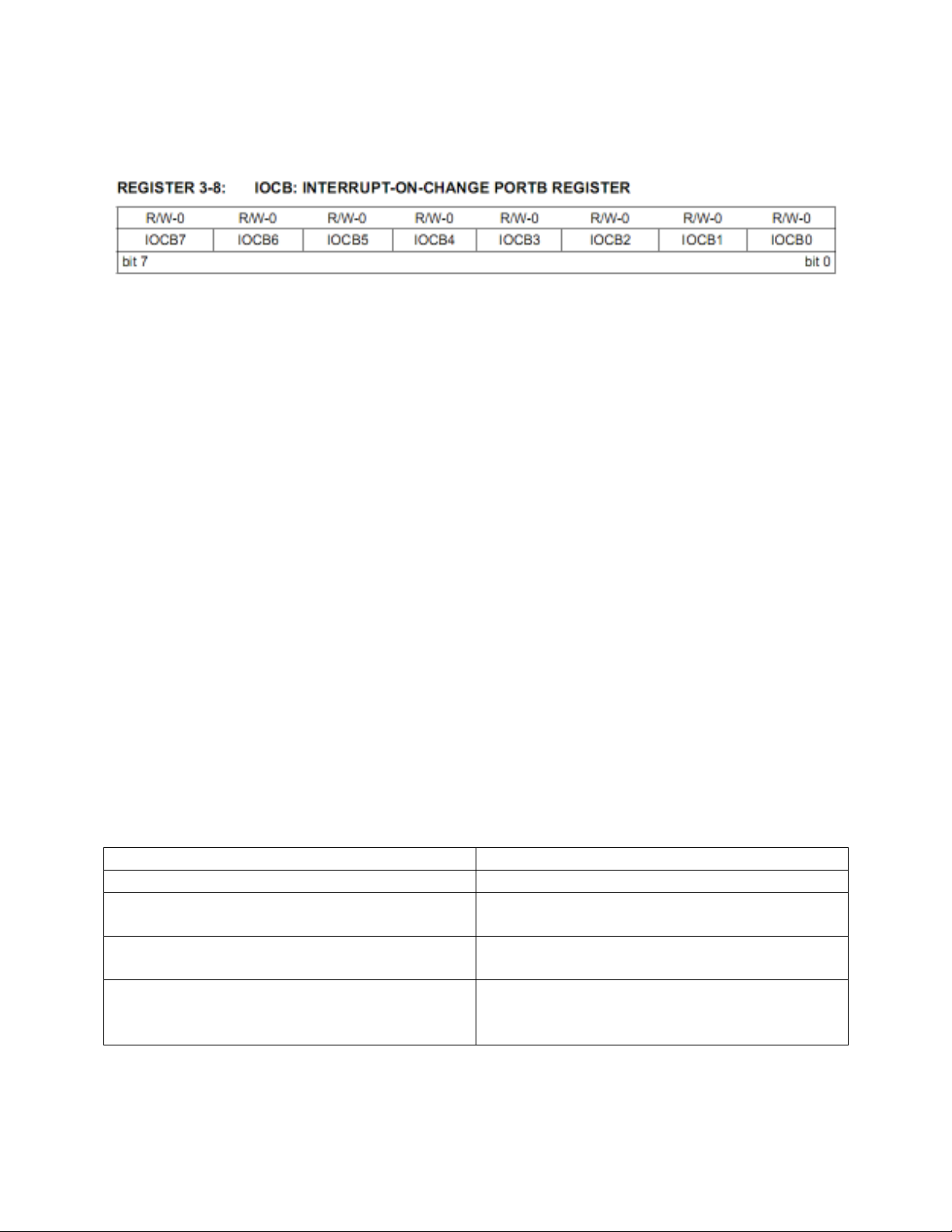

4.3.Ngắt on-change ở PORTB:

Ngoài ngắt INT chỉ có duy nhất ở chân RB0 , thì cả PORTB (từ RB0 đến RB7) còn hỗ trợ

ngắt on-change , ngắt on-change xảy ra khi tín hiệu logic ở chân của PORTB thay đổi trạng thái

logic.

Sơ đồ ngắt on-change:

Giáo trình thí nghiệm vi điều khiển ứng dụng

5

Các thanh ghi và các bit điều khiển ngắt on-change :

IOCBX=0 : Không cho phép ngắt on-change ở chân thứ X của PORTB.

IOCBX=1 : Cho phép ngắt on-change ở chân thứ X của PORTB.

Các bit khởi tạo khác :

RBIF : Cờ ngắt on-change ở PORTB, cần phải xóa bít này trong lập trình.

RBIE : Bit cho phép ngắt on-change của PORTB.

GIE : Bit cho phép ngắt toàn cục.

Các bước khởi tạo ngắt on-change :

Bước 1 : Khởi tạo PORTB là ngõ vào số , có điện trở treo.

Bước 2 : Khởi tạo ngắt on-change ở PORTB

IOCB=0xFF; //khởi tạo toàn bộ PORTB ngắt on-change(có thể khởi tạo

một hay cả PORTB).

RBIE=1; //Cho phép ngắt xảy ra .

RBIF=0; //Xóa cờ ngắt

GIE=1; //Cho phép ngắt toàn cục

Chú ý : Đối với ngắt on-change , việc xóa cờ ngắt (RBIF=0) không đủ để cho lần ngắt

tiếp theo được thực hiện , mà còn phải thêm điều kiện đọc hoặc viết vào thanh ghi PORTB.

Ví dụ :

unsigned char bien ;

bien = PORTB ; //đọc thanh ghi PORTB.

hoặc PORTB =5 ; //viết vào thanh ghi PORTB

4.4.Bảng so sánh giữa ngắt INT và ngắt on-change :

Ngắt ở chân INT(RB0)

Ngắt on-change

Chí có duy nhất ở chân RB0

Xảy ra trên cả PORTB

Để xảy ra ngắt thì tín hiệu logic là cạnh lên

hoặc cạnh xuống.

Chỉ cần tín hiệu logic thay đổi là xảy ra ngắt,

không phân biệt cạnh lên hay cạnh xuống.

Các bit khởi tạo :

INTE , INTF , INTEDG , GIE

Các bit khởi tạo :

IOCBx , RBIE , RBIF , GIE

Để cho lần ngắt tiếp theo được thực hiện thì

cần phải xóa cờ ngắt INTF.

Để cho lần ngắt tiếp theo được thực hiện thì

cần phải xóa cờ ngắt INTF và đọc ( hoặc ghi)

vào thanh ghi PORTB.