Xung & Hoi1

1.Giớithiệu

2.Sơđồ khốivàchân(block and pin diagrams)

3.Tổchứcbộnhớ

4.Cácthanhghichứcnăng đặcbiệt(SFR)

5.Dao độngvàhoạtđộngreset

6.Tậplệnh

7.Cácmode định địachỉ

8.LậptrìnhIO

9.Tạotrễ

10.LậptrìnhTimer/Counter

11.Lậptrìnhgiaotiếpnốitiếp

12.Lậptrìnhngắt

13.Lậptrìnhhợpngữ

Xung & Hoi2

2

2

-

-

1.

1. Sơ

Sơđ

đồ

ồkh

khố

ối

i

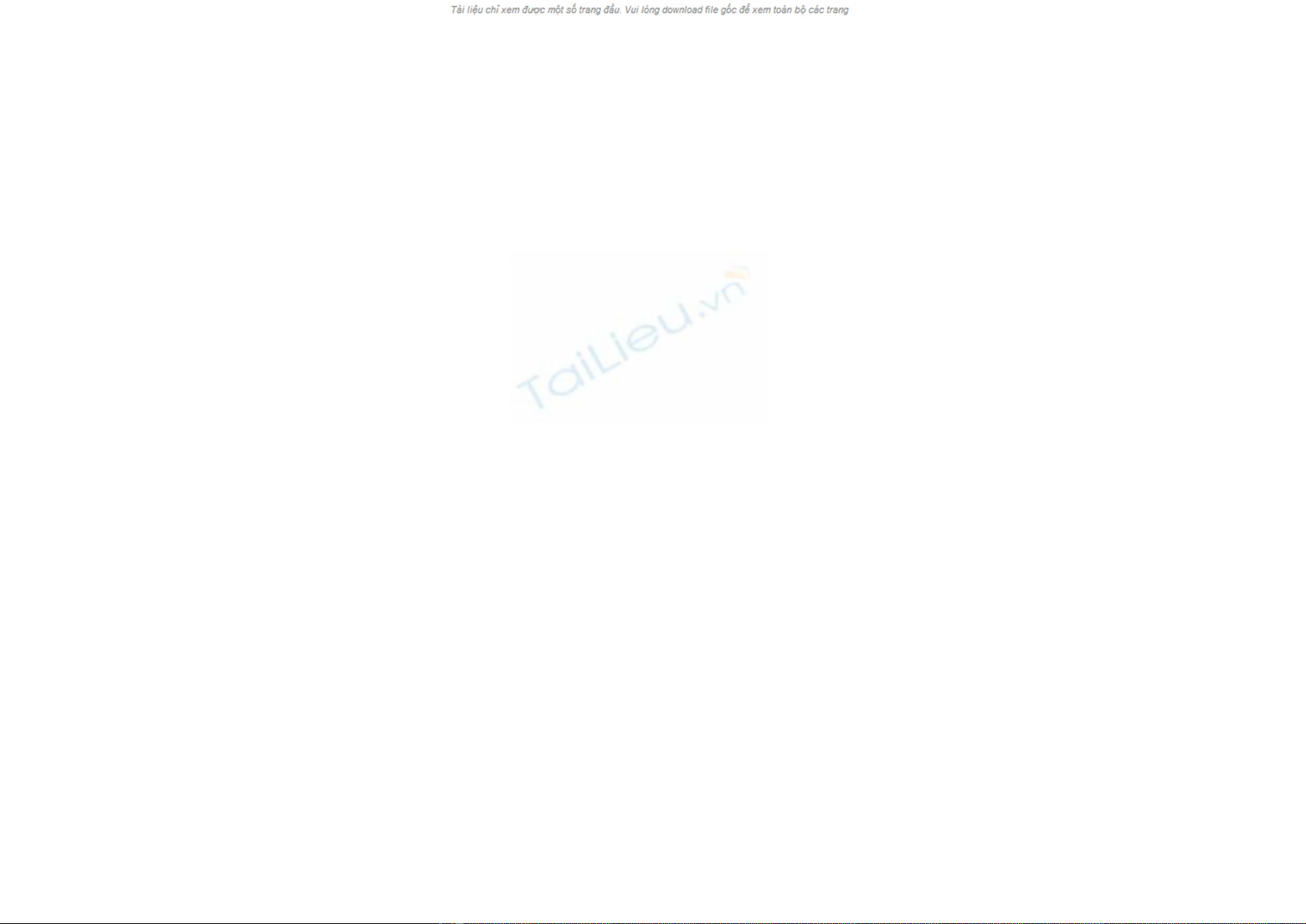

CPU

On-chip

RAM

On-chip

ROM for

program

code

4 I/O Ports

Timer 0

Serial

Port

OSC

Interrupt

Control

External

by Timers, Serial Port

Timer 1

Timer/Counter

Bus

Control

TxDRxD

P0 P1 P2 P3

Address/Data

Counter

Inputs

T1,T0

/EA

RST ALE

/PSEN

Xung & Hoi3

2

2

-

-

2. So

2. So s

sá

ánh

nh c

cá

ác

cth

thà

ành

nh viên

viên h

họ

ọ8051

8051

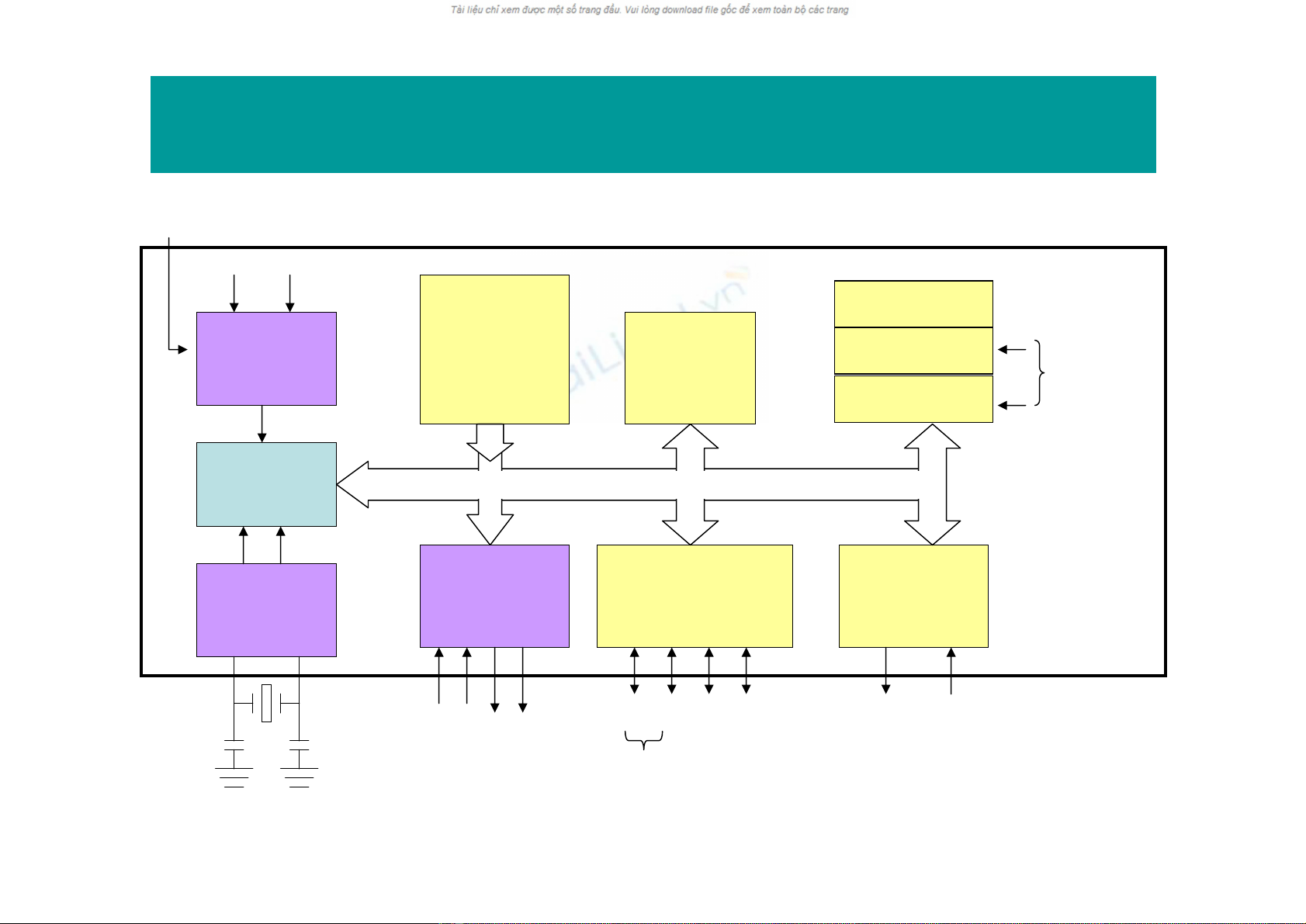

5

1

32

2

128

4K

Flash

8951

5

1

32

2

128

4K

EPROM

8751

5

1

32

2

128

0K

8031

665Interrupt

sources

111Serial Port

323232I/O pins

332Timers

256256128Data Mem on

chip (bytes)

8K

EPROM

8K

ROM

4K

ROM

Code Mem on

chip (bytes)

875280528051Specification

Xung & Hoi4

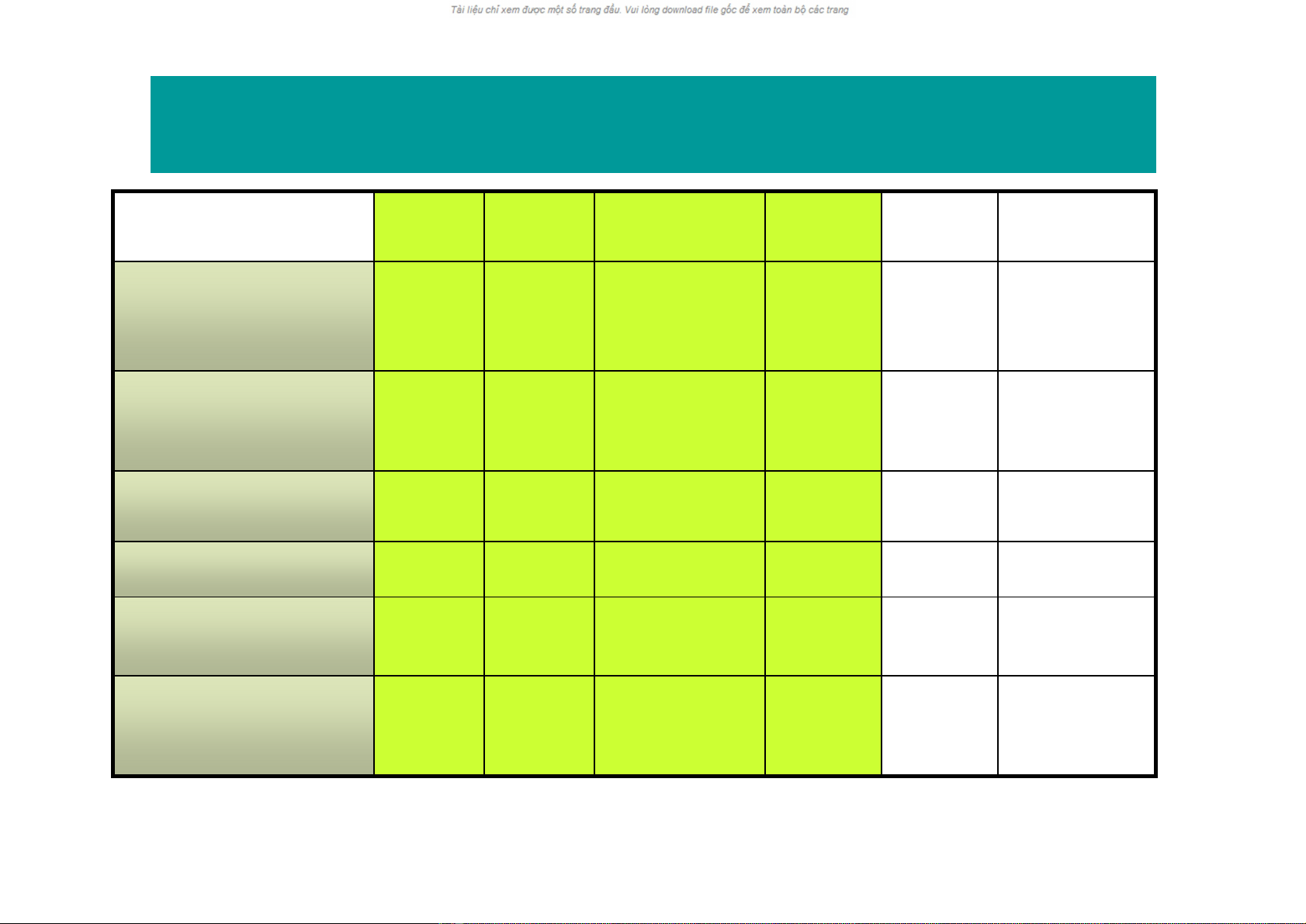

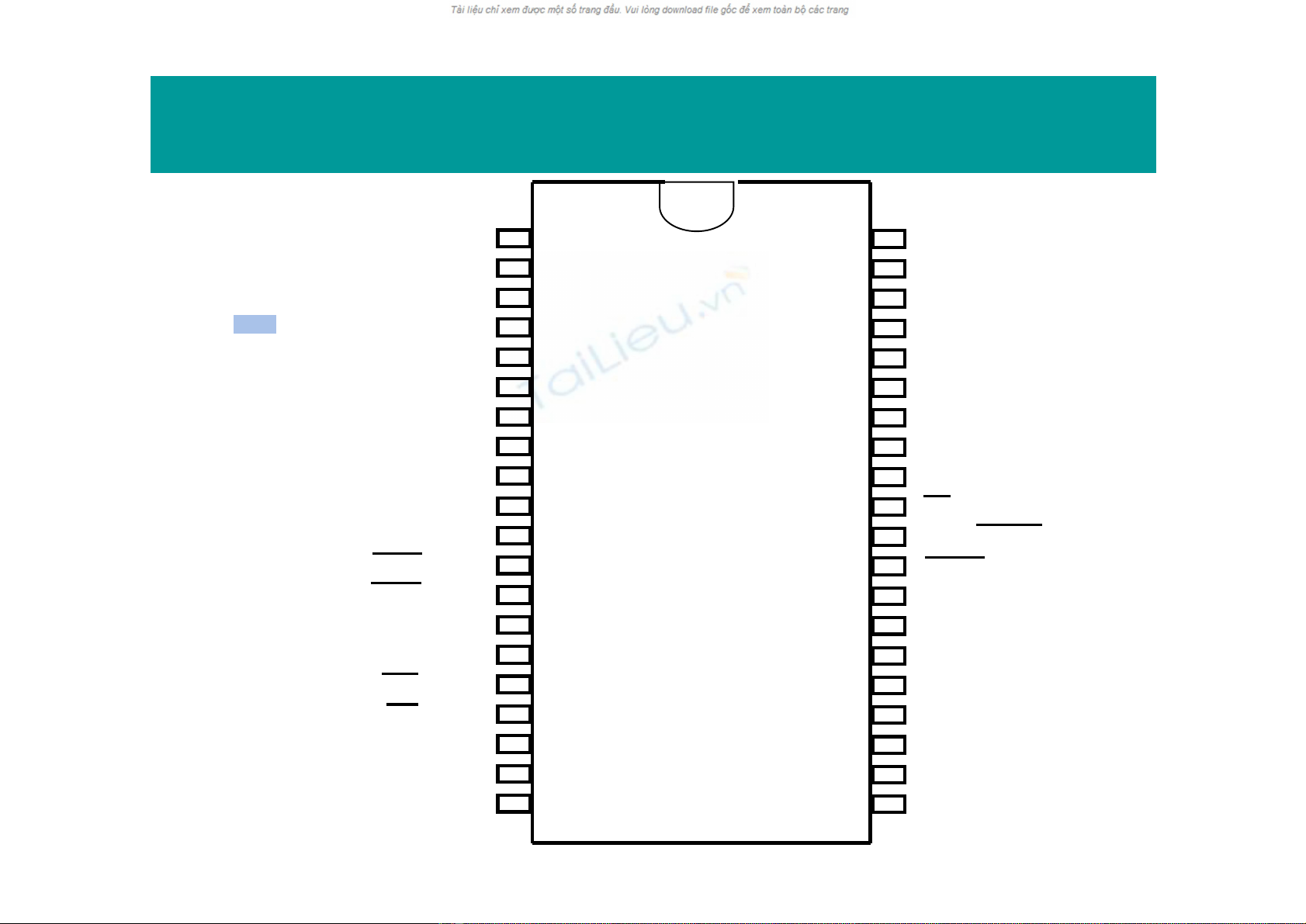

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RST

(RXD)P3.0

(TXD)P3.1

(T0)P3.4

(T1)P3.5

XTAL2

XTAL1

GND

(INT0)P3.2

(INT1)P3.3

(RD)P3.7

(WR)P3.6

Vcc

P0.0(AD0)

P0.1(AD1)

P0.2(AD2)

P0.3(AD3)

P0.4(AD4)

P0.5(AD5)

P0.6(AD6)

P0.7(AD7)

EA/VPP

ALE/PROG

PSEN

P2.7(A15)

P2.6(A14)

P2.5(A13)

P2.4(A12)

P2.3(A11)

P2.2(A10)

P2.1(A9)

P2.0(A8)

8051

2

2-

-3.

3. Sơ

Sơđ

đồ

ồchân

chân

Xung & Hoi5

C

C

á

á

c

c

chân

chân 8051 (

8051 (ph

phầ

ần

n1)

1)

§Vcc (chân40):

üCungcấpnguồnchochip

ü+5V

§GND (chân20): đất

§XTAL1 & XTAL2 (chân19, 18)

ü2 châncungcấpxungclock ngoài

üCách1: dao độngdùngthạchanh

üCách2: dao độngtừnguồnxungclock TTL bênngoài

üQuanhệgiữachukỳmáyvàXTAL

![Ngân hàng câu hỏi thi giữa kì môn Truyền động điện [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/42601758354546.jpg)

![Câu hỏi ôn tập Quy trình an toàn điện có đáp án [kèm đáp án chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/18761758354548.jpg)

![Đề thi trắc nghiệm Kỹ thuật mạch điện tử: Tổng hợp [Năm]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/23481758356189.jpg)

![Tài liệu ôn tập Thông tin quang [năm] [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250917/anvunguyen0207@gmail.com/135x160/56551758168054.jpg)