Khoa KTMT Vũ Đ c Lungứ1

Ch ng 7: Máy tr ng tháiươ ạ

Ch ng 7: Máy tr ng tháiươ ạ

Máy tr ng thái ki u Mooreạ ể

Máy tr ng thái ki u Mealyạ ể

Khoa KTMT Vũ Đ c Lungứ2

Khái ni m máy tr ng tháiệ ạ

Khái ni m máy tr ng tháiệ ạ

H tu n t ệ ầ ự ~ Máy tr ng thái thu t toán (algorithmic state ạ ậ

machine) ~ Máy tr ng thái (State Machine - SM)ạ

–Gi n đ tr ng tháiả ồ ạ

–L u đ SMư ồ

Dùng đi u khi n m t HTS th c hi n t ng b c m tề ể ộ ự ệ ừ ướ ộ

State Machine

MOORE

Q+ = f(Q,X)

Z = g(Q)

MEALY

Q+ = f(Q,X)

Z = g(Q, X)

Khoa KTMT Vũ Đ c Lungứ3

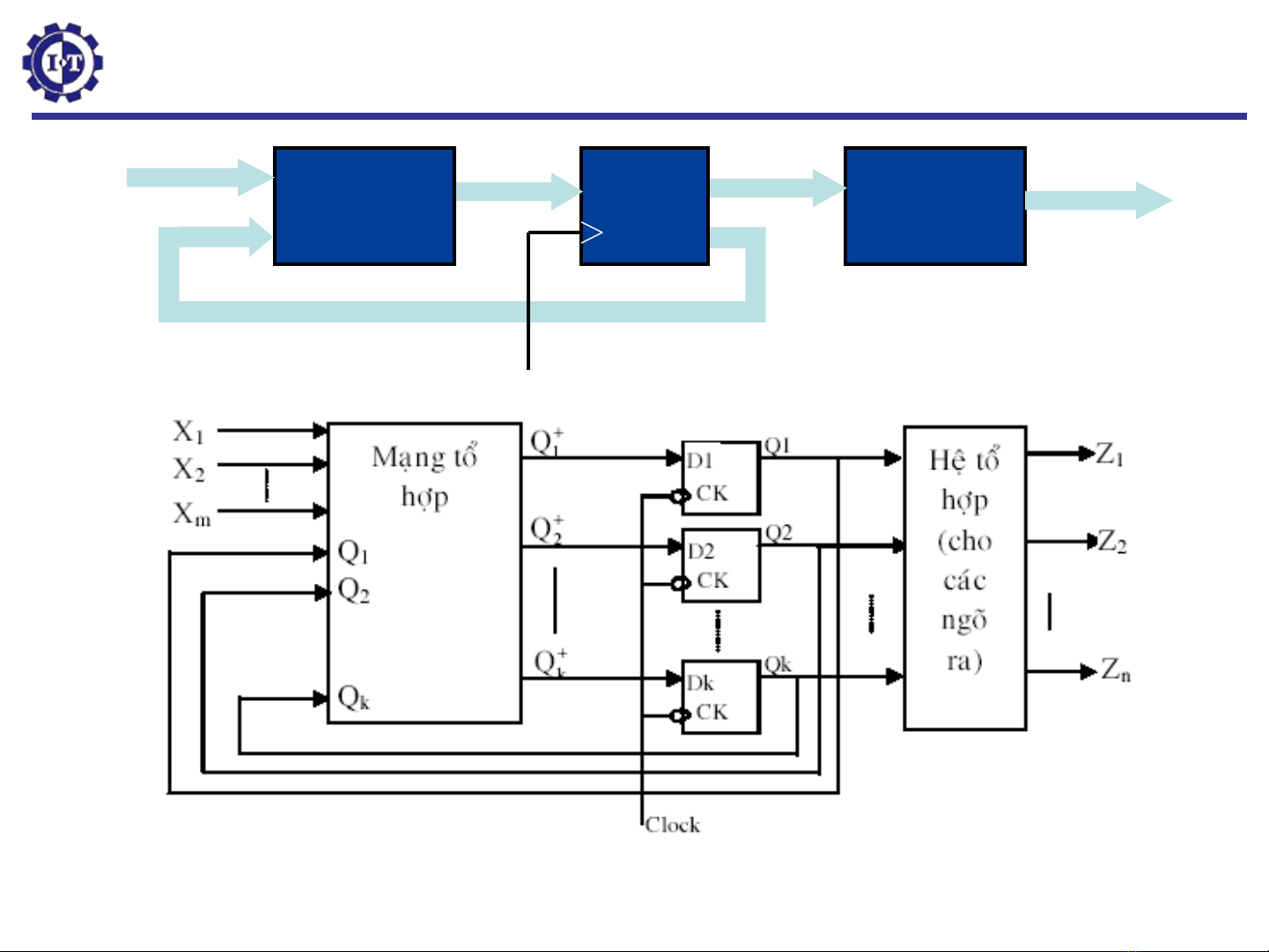

Máy MOORE

Máy MOORE

M ch Logic ạ

M ch Logic ạ

t h pổ ợ

t h pổ ợ M ch Logic ạ

t h pổ ợ

FF

Clock

X

XZ

Z

Khoa KTMT Vũ Đ c Lungứ4

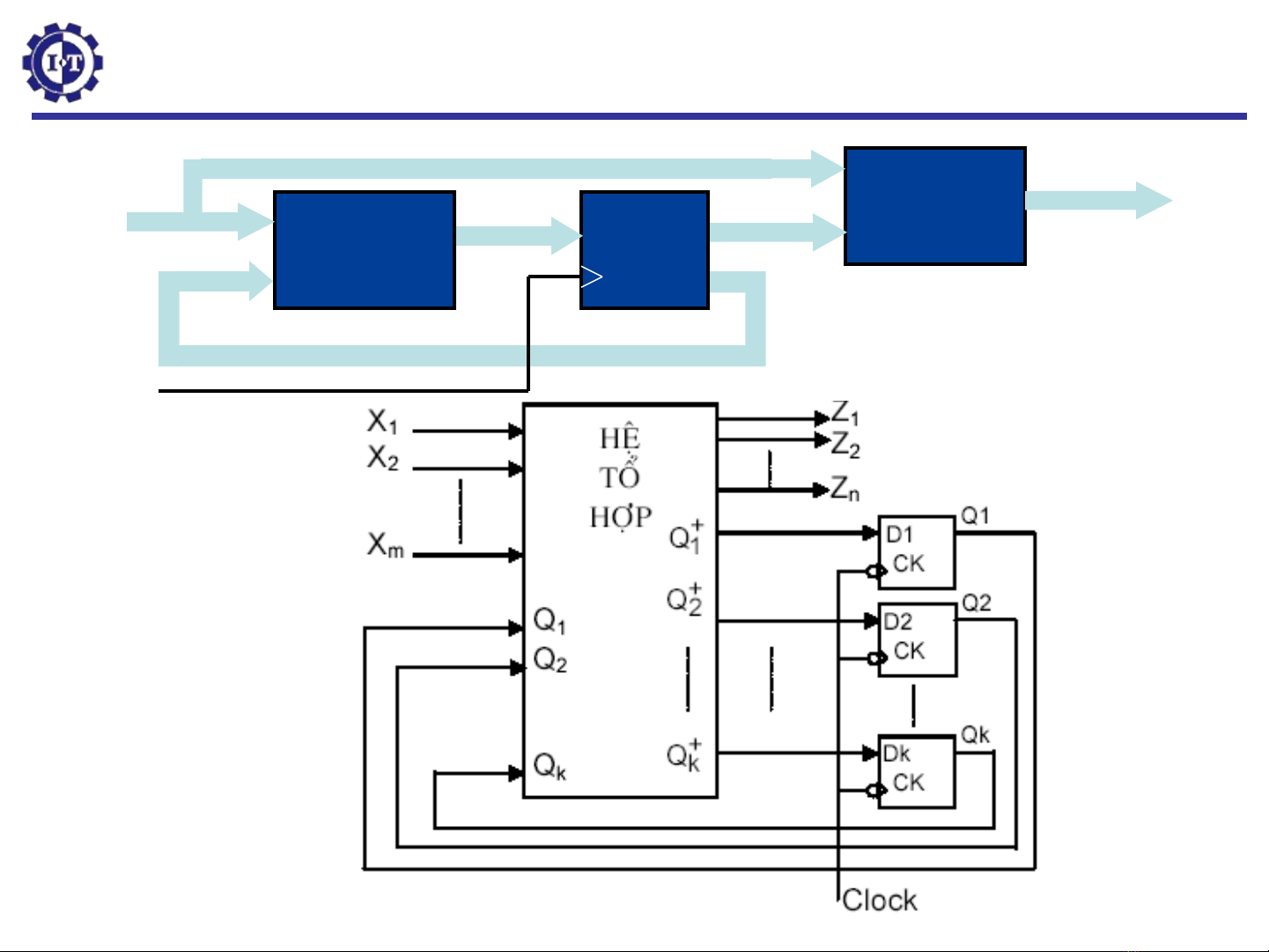

Máy MEALY

Máy MEALY

M ch Logic ạ

t h pổ ợ

M ch Logic ạ

t h pổ ợ

FF

Clock

X

XZ

Z

Khoa KTMT Vũ Đ c Lungứ5

L u đ máy tr ng tháiư ồ ạ

L u đ máy tr ng tháiư ồ ạ

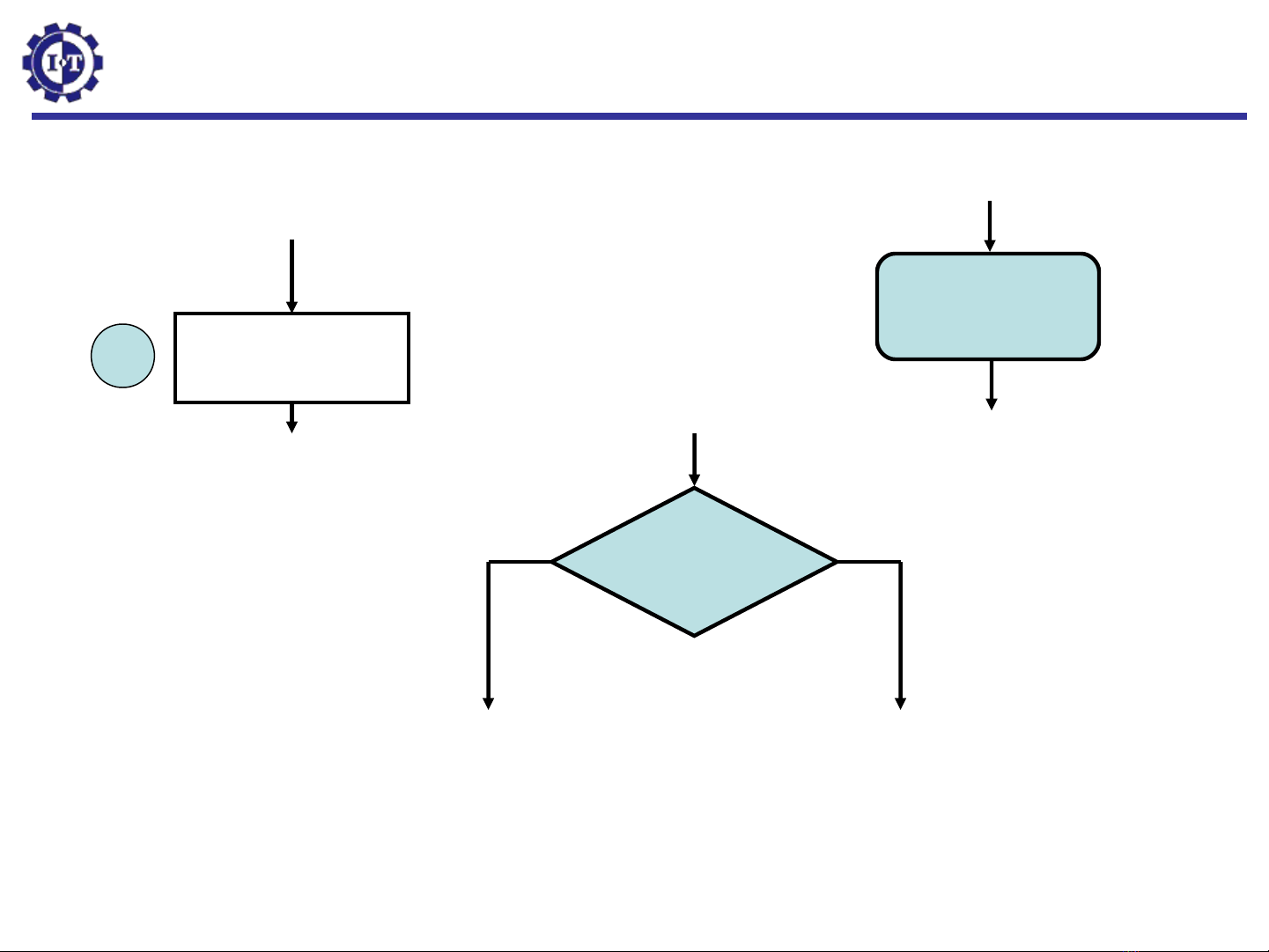

Các thành ph n chính c a l u đ SMầ ủ ư ồ

Output List

010

S0

Đi u ki nề ệ

X

10

H p tr ng tháiộ ạ

H p đi u ki nộ ề ệ

Output list

H p xu t theo đi u ki nộ ấ ề ệ

![SCADA, DCS: Tìm hiểu và ứng dụng trong công nghiệp [A-Z]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130701/lilinz/135x160/5571372680022.jpg)

![DCS và SIS: Khái niệm và Thực tiễn [Cập nhật mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130623/sea123123/135x160/1504773_269.jpg)

![Giáo trình Tự động hóa quá trình sản xuất: Phần 2 [Đầy đủ/Chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/6191777378796.jpg)

![Giáo trình Kỹ thuật Vi điều khiển Phần 2: [Mô tả nội dung phần 2 nếu có]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/62641777433528.jpg)

![Giáo trình Kỹ thuật Vi điều khiển Phần 1: [Mô tả chi tiết hơn về nội dung phần 1 nếu có thông tin]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260424/vispacex_27/135x160/15221777433529.jpg)