CHƯƠNG 6 – PHẦN 1

NHẬP MÔN MẠCH SỐ

Mạch tuần tự: Chốt và Flip-flop

(Sequential circuit: Latches and Flip-flop)

Nội dung

1. S-R chốt (latch)

2. D chốt

3. D Flip-flop

4. T Flip-flop

5. S-R Flip-flop

6. J-K Flip-flop

7. Scan Flip-flop

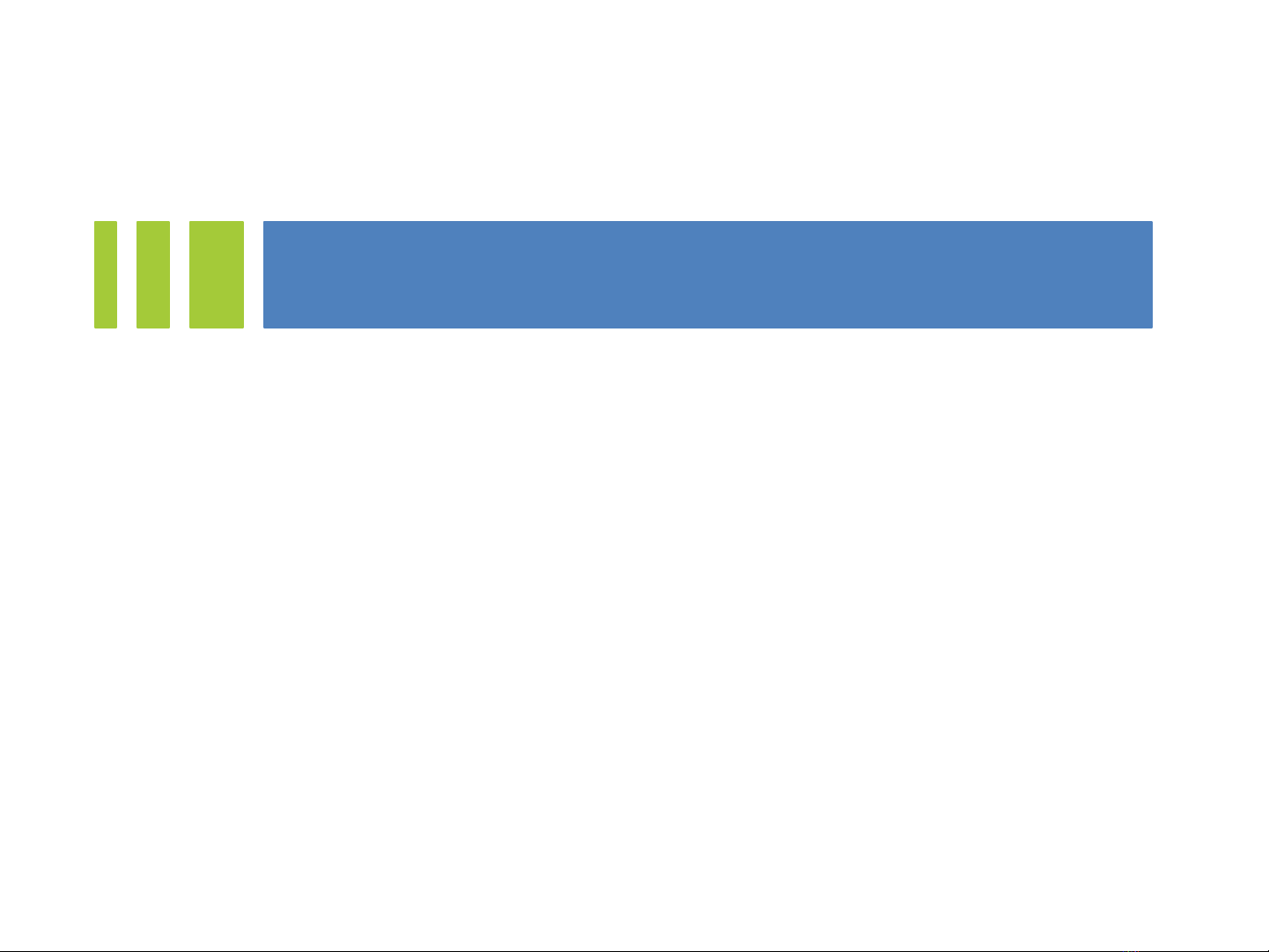

1. S-R chốt (Set-Reset latch)

S-R chốt dùng cổng NOR

Mạch logic Bảng chức năng

Ký hiệu

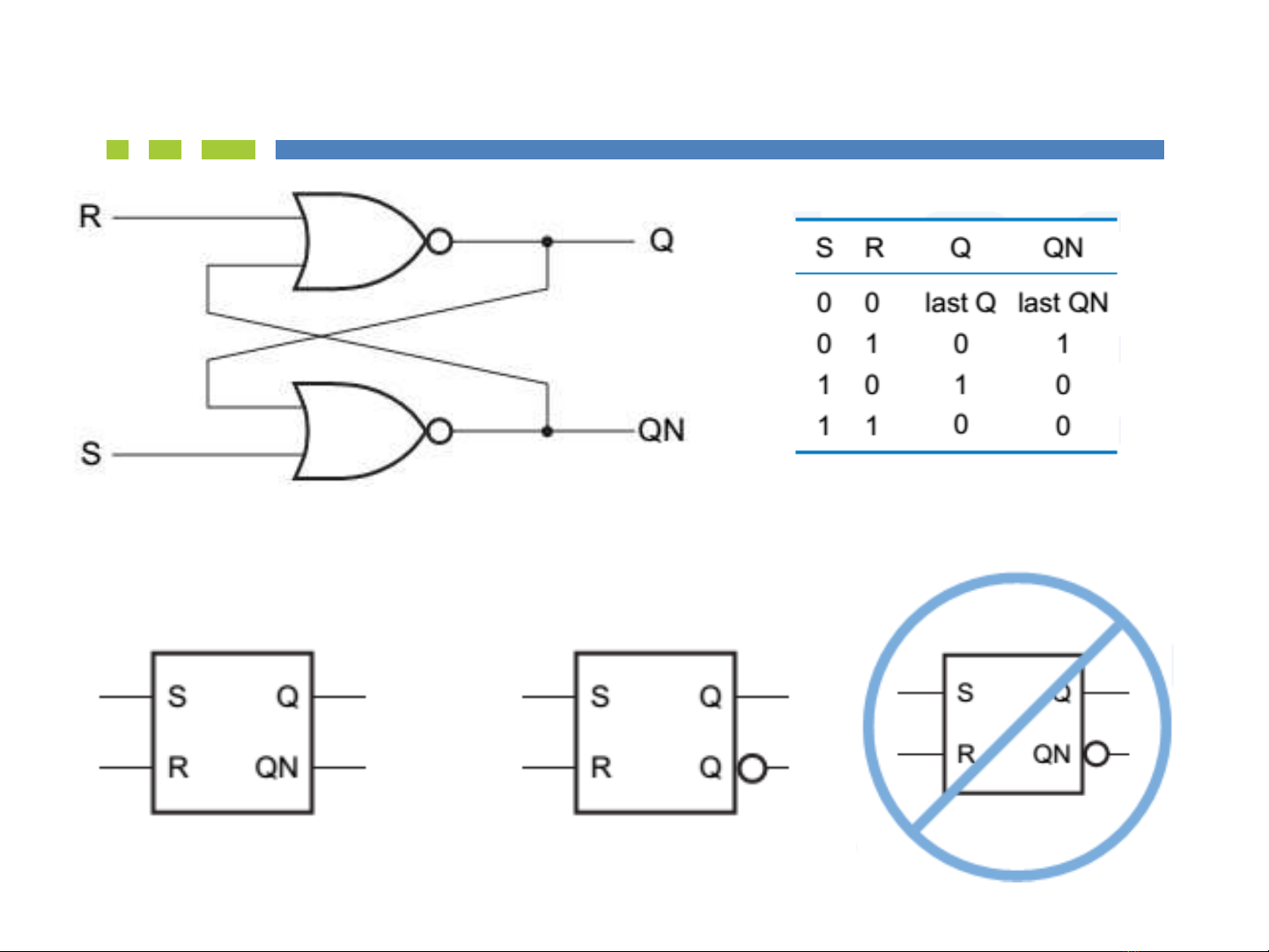

Ngõ vào thông thường

S và R chuyển từ mức 1 xuống mức 0 đồng thời

S-R chốt dùng cổng NOR

![Bài giảng Nhập môn mạch số: Chương 3 (Phần 2) - TS. Trịnh Lê Huy [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/38491750824827.jpg)

![Bài giảng Nhập môn Kỹ thuật điện [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251208/nguyendoangiabao365@gmail.com/135x160/60591765176011.jpg)