1

Chương 5

Thiếtkếhệvi xửlý

2

Nội dung

•Giảimãđịachỉ

•Giaotiếpbộnhớ

•Giaotiếpvới khóa (switch) va bàn phím

•Giaotiếpbô hiểnthi (Display)

–GiaotiếpvớiLED

–GiaotiếpvớiLCD

•Giaotiếp A/D-D/A

3

5.1 Giảimãđịachỉ

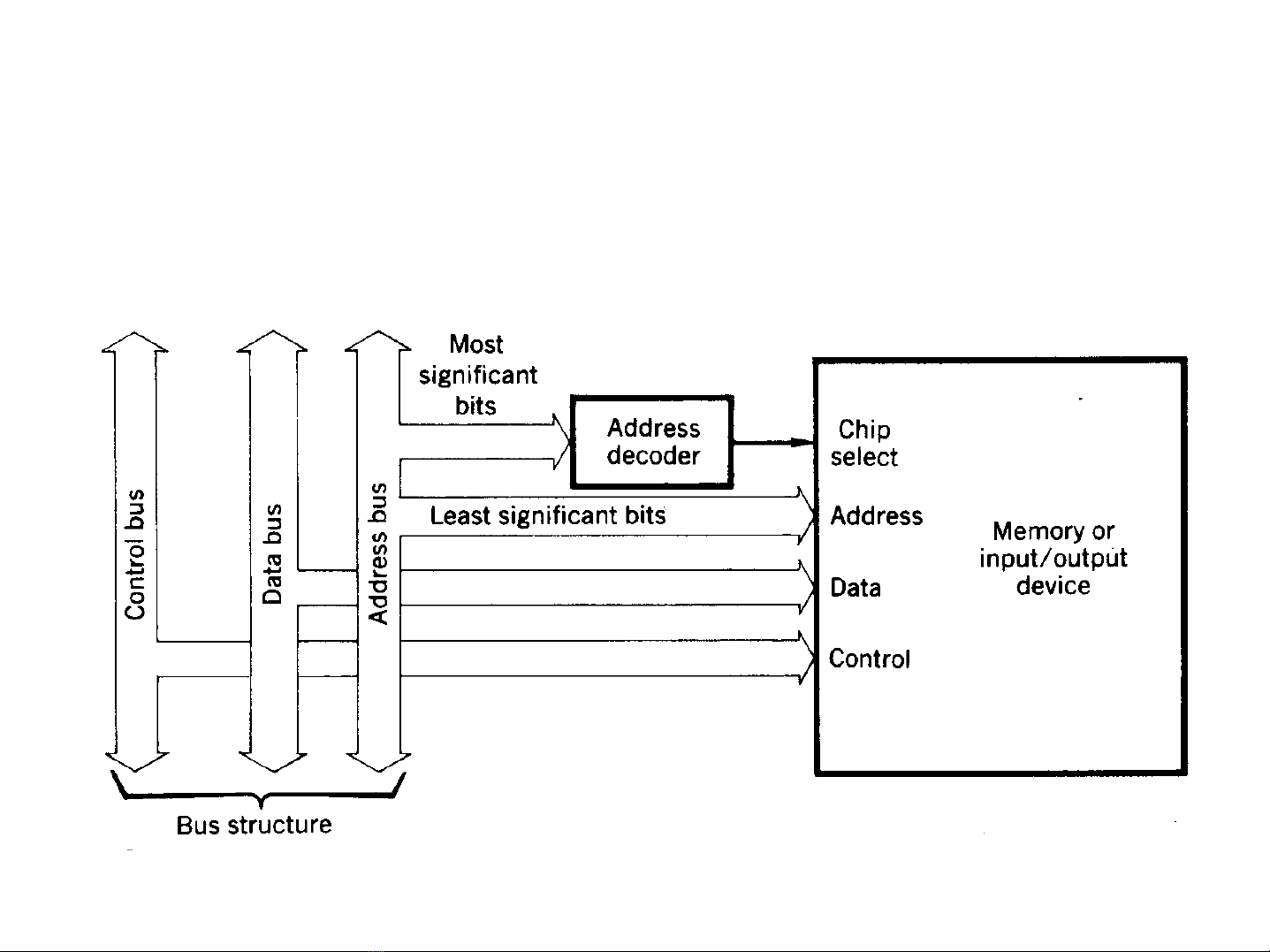

• Khi vi xửlý gửimộtđịachỉra bus địachỉ, thì thông tin này phảiđược chuyển

thành lệnh cụthểcho thiếtbịcụthể. Giảimãđịachỉthựchiệntácvụnày. Nó sử

dụng thông tin bus địachỉđểxác định thiếtbịnào sẽđượctruycập.

4

Phương pháp giảimãđịachỉ

Có 2 phương pháp giảimãđịachỉ:

1. Giảimãtoànphần (Full address decoding): Mỗi

ngoạivi được gán cho mộtđịachỉduy nhất. Tấtcả

các bit địachỉđượcdùngđể định nghĩavịtrí được

tham chiếu.

2. Giảimãmộtphần (Partial address decoding): Không

phảitấtcảcác bit được dùng cho việcgiảimãđịachỉ.

Các ngoại vi có thểđáp ứngchotrênmộtđịachỉ.

Phương pháp làm giảmđộ phứctạptrongmạch giải

mã địachỉ. Thông thường các hệthống nhỏsửdụng

giảimãmộtphần.

5

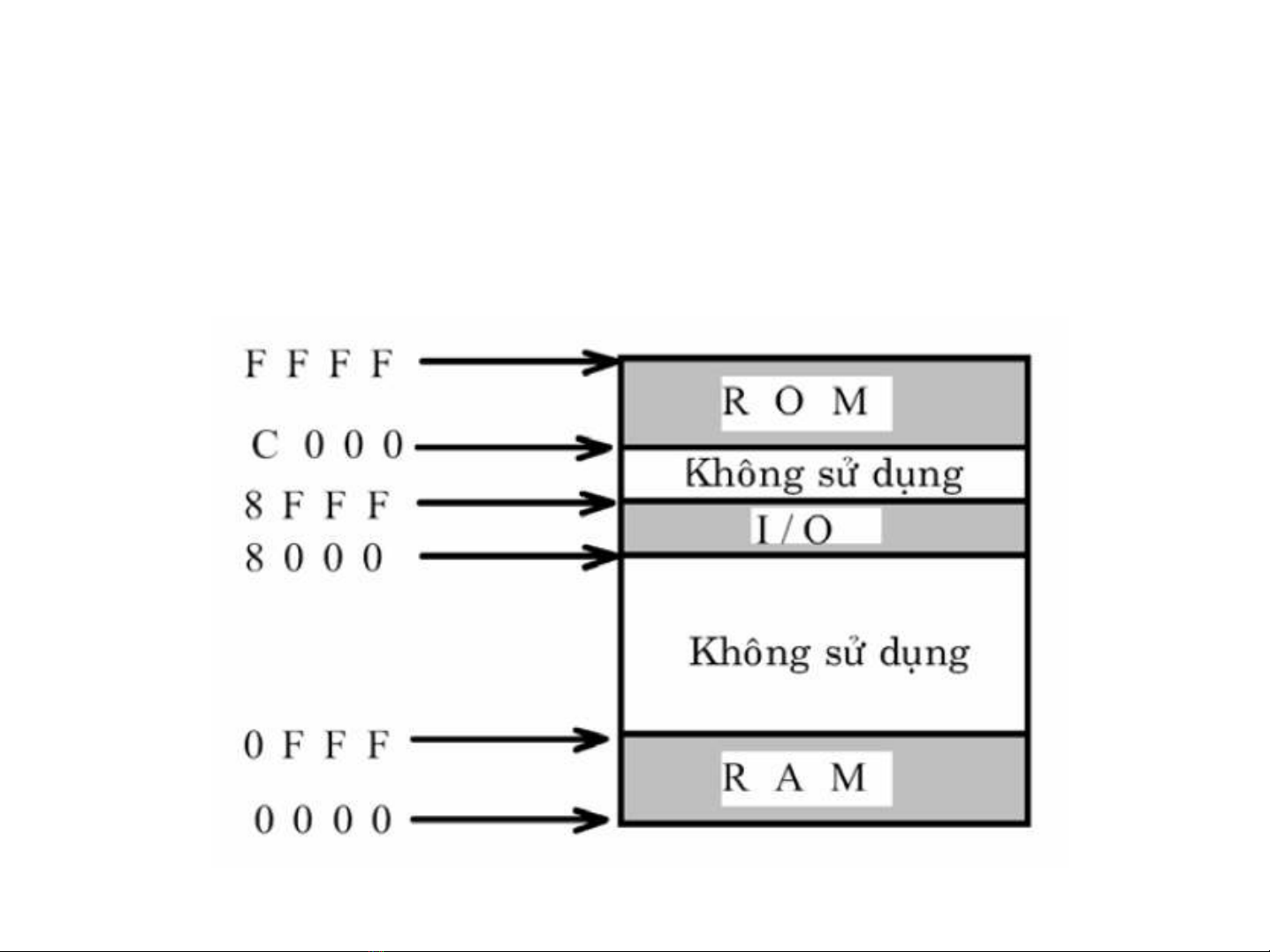

Thí dụ: TK mạch giải mã địa chỉ

•Vớibảng bộnhớsau, hãy thiếtkếmạch giảimãtoànphầnvà

mạch giảimãmộtphần cho các chip bộnhớ(RAM 4KB và

ROM 16KB) và I/O

![Bài giảng Kiến trúc máy tính: Chương 1 - Giới thiệu tổng quan [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250729/kimphuong1001/135x160/47331753774510.jpg)