CỘNG HOÀ XÃ HỘI CHỦ NGHĨA VIỆT NAM

Độc lập - Tự do - Hạnh phúc

ĐỀ THI TỐT NGHIỆP CAO ĐẲNG NGHỀ KHOÁ 3 (2009 - 2012)

NGHỀ: ĐIỆN TỬ CÔNG NGHIỆP

MÔN THI: LÝ THUYẾT CHUYÊN MÔN NGHỀ

Mã đề thi: ĐTCN - LT 16

Hình thức thi: Viết

Thời gian: 180 Phút (Không kể thời gian chép/ giao đề thi)

ĐỀ BÀI

Câu 1 (2điểm):

Phân tích, thiết kế bộ mã hóa 8 đầu vào - 3 đầu ra sử dụng cổng logic. Ứng với

một đầu vào tích cực là một mã ngõ ra.

Câu 2 (2điểm):

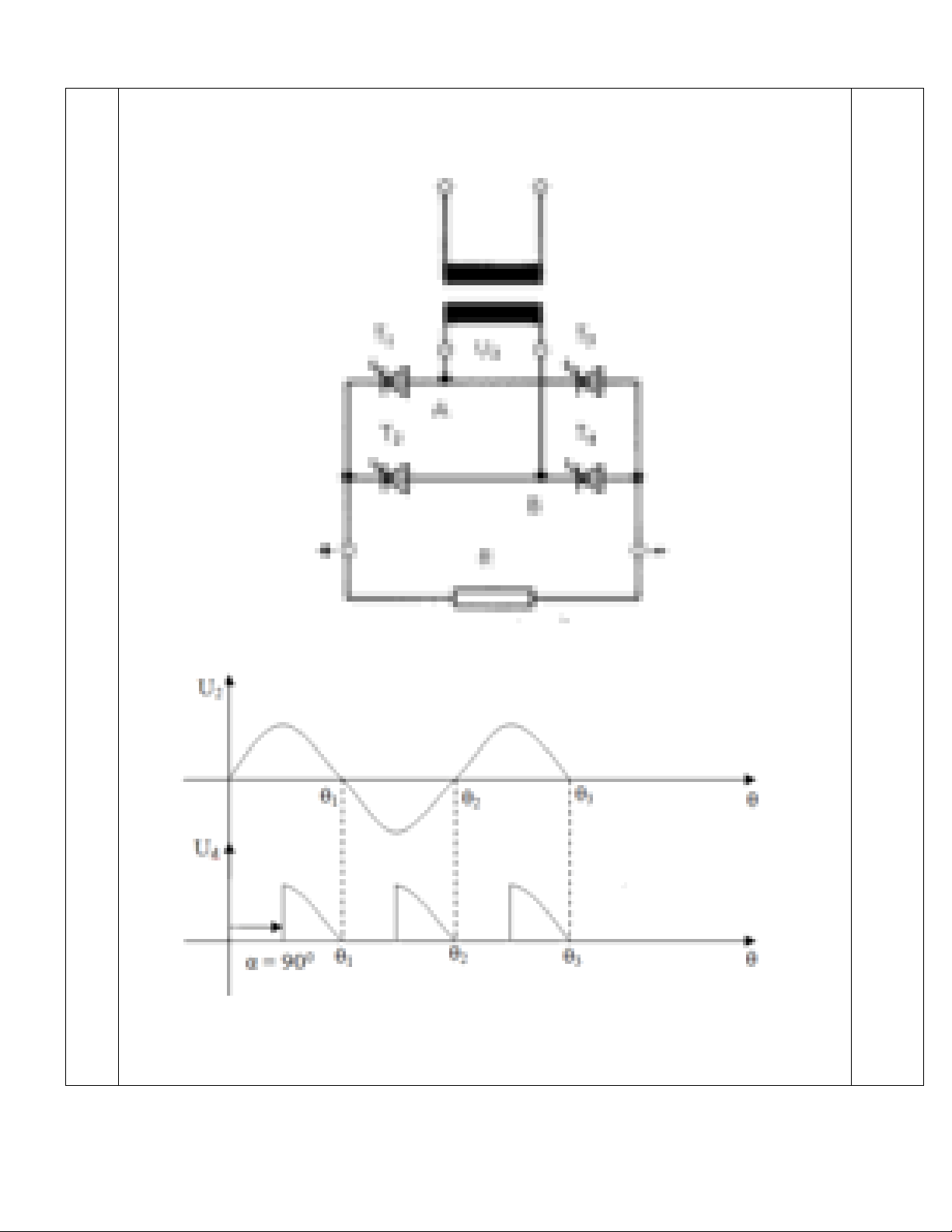

Cho mạch chỉnh lưu cầu một pha có điều khiển, biên độ áp vào cực đại 300V,

góc kích α = 900, tải thuần trở R.

a. Vẽ sơ đồ mạch và dạng sóng điện áp vào, điện áp ra trên tải.

b. Tính điện áp ra trung bình trên tải.

Câu 3 (3điểm):

Trình bày các chế độ hoạt động của timer trong vi điều khiển. Viết chương

trình sử dụng timer tạo đồng thời hai xung vuông 1KHz và 500 Hz tại 2 chân P0.0 và

P0.1 của vi điều khiển. Biết vi điều khiển có bộ dao động ngoài tần số thạch anh là

12MHz.

Câu 4 (3điểm): (phần tự chọn, các trường tự ra đề)

………………., ngày ……. tháng ……. năm …………

Duyệt Hội đồng thi tốt nghiệp Tiểu ban ra đề thi

1

CỘNG HOÀ XÃ HỘI CHỦ NGHĨA VIỆT NAM

Độc lập - Tự do - Hạnh phúc

ĐÁP ÁN

ĐỀ THI TỐT NGHIỆP CAO ĐẲNG NGHỀ KHOÁ 3 (2009 - 2012)

NGHỀ: ĐIỆN TỬ CÔNG NGHIỆP

MÔN THI: LÝ THUYẾT CHUYÊN MÔN NGHỀ

Mã đề thi: DA ĐTCN - LT 16

Câu

NỘI DUNG ĐIỂM

I. Phần bắt buộc

1

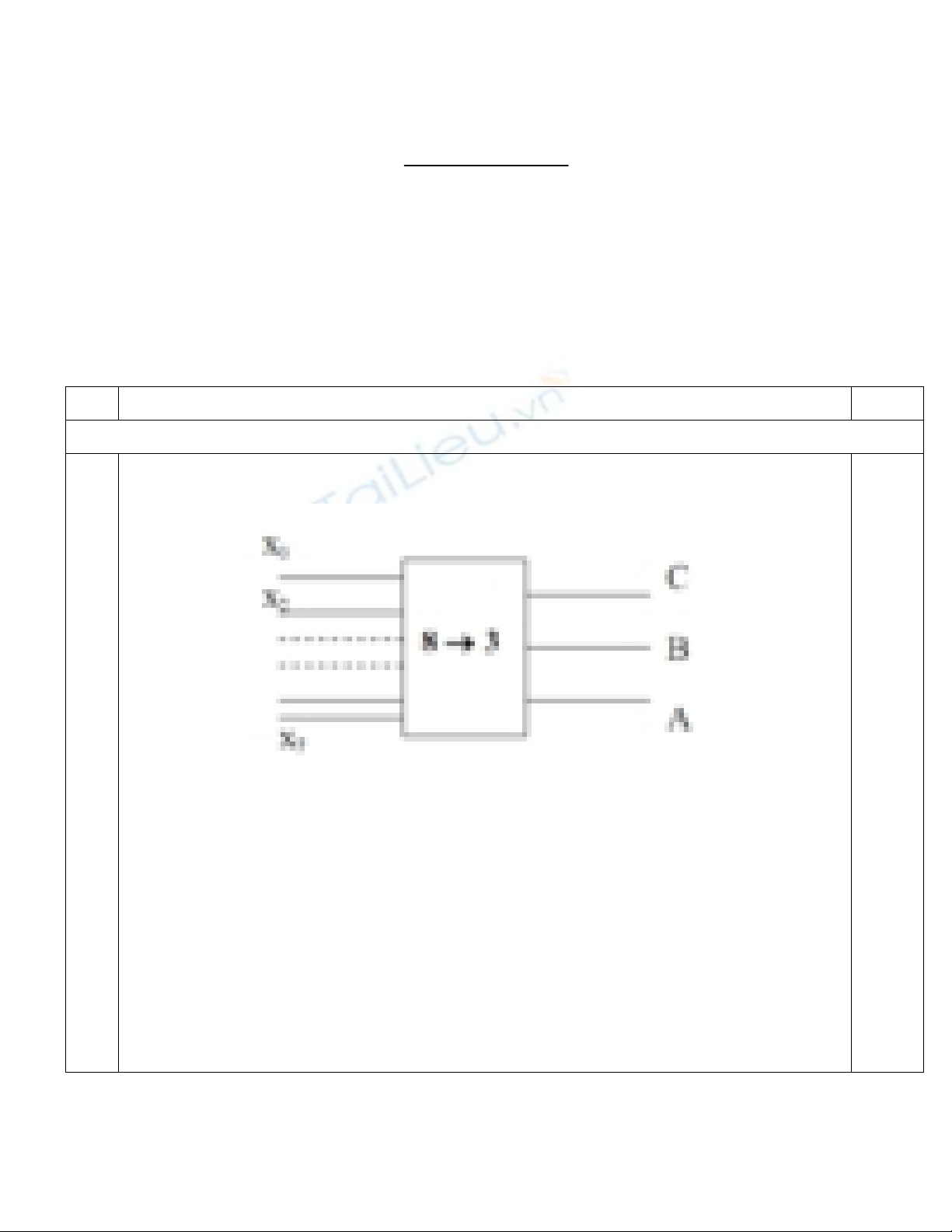

Xét mạch mã hóa nhị phân từ 8 sang 3 ( 8 ngõ vào, 3 ngõ ra).

Trong đó:

X0, X1, ….,X7 là các ngõ vào tín hiệu

A, B, C là các ngõ ra

Mạch mã hóa nhị phân thực hiện biến đổi tín hiệu ngõ vào thành một từ mã

nhị phân tương ứng ở ngõ ra, cụ thể như sau

0→ 000 2→ 010 4→ 100 6 → 110

1→ 001 3→ 011 5→ 101 7 → 111

Chọn mức tác động (tích cực) ở ngõ vào là mức logic 1, ta có bảng trạng

thái mô tả hoạt động của mạch bảng 4.1:

0,5

đ

0,5đ

2

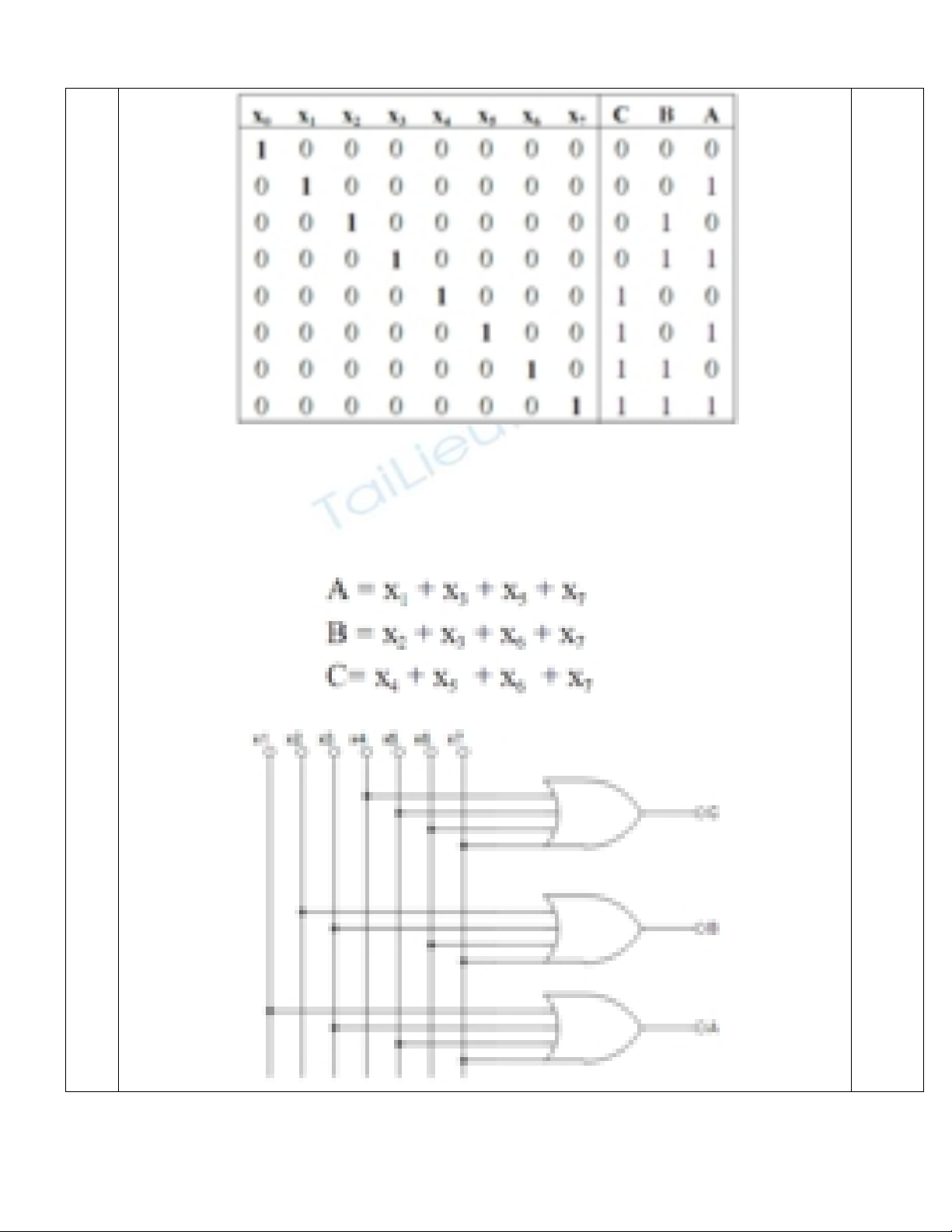

Giải thích bảng trạng thái: Khi một ngõ vào ở trạng thái tích cực (mức logic

1) và các ngõ vào còn lại không được tích cực (mức logic 0) thì ngõ ra xuất hiện

từ mã tương ứng. Cụ thể là: khi ngõ vào x0=1 và các ngõ vào còn lại bằng không

thì từ mã ở ngõ ra là 000, khi ngõ vào x1=1 và các ngõ vào còn lại bằng không thì

từ mã ở ngõ ra là 001, vv…

Phương trình logic tối giản:

Sơ đồ logic

0,5đ

0,5đ

3

2 a. Sơ đồ mạch và dạng sóng điện áp vào, điện áp ra trên tải

+ Sơ đồ mạch

+ Dạng sóng điện áp vào, điện áp ra trên tải

b. Điện áp ra trung bình trên tải

0,75

đ

0,75đ

0,5đ

4

Ud = U2(1+cos ) = .300(1+cos900) = .300(1+0) = 135V

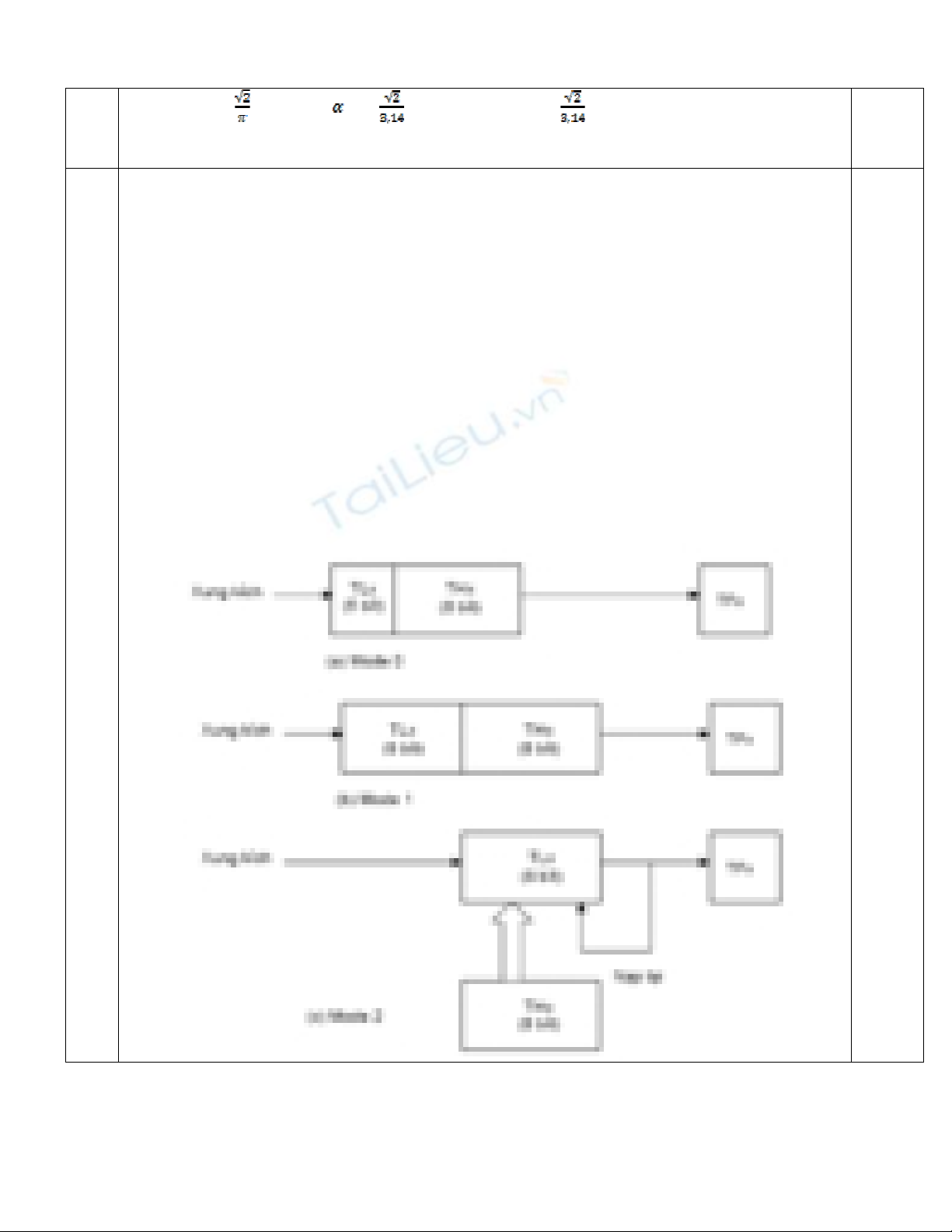

3 - Chế độ timer 13 bít (mode 0)

Chế độ này nhằm tương thích vớI họ vi điều khiển trước của 8051 là 8048

(hình4.2a). Trong chế độ này thanh ghi định thờI byte cao THx được nốI tiếp vớI

5 bít thấp của thanh ghi TLx để tạo thành bộ định thờI 13 bít, 3 bít cao của TLx

không dùng.

- Chế độ timer 16 bít (mode 1)

Cũng giống như mode 0, xung đồng hồ được đưa vào cặp thanh ghi định

thời TLx/THx, khi có xung đồng hồ timer sẻ đếm lên từ 0000H, 0001H,

0002H…Hiện tượng tràn sẻ xảy ra khi số đếm từ giá trị FFFFH chuyển sang

0000H và sẻ làm cờ tràn bị set và timer tiếp tục đếm.

Cờ tràn là biến TFx trong thanh ghi điều khiển TCON, cờ này được đọc và

ghi bằng phần mềm. Bít có giá trị cao nhất của timer là bít 7 trong thanh ghi THx

và bít

thấp nhất blà bít 0 trong thanh ghi TLx, cặp thanh ghi định thờI TLx/THx có thể

được đọc hoặc ghi bằng phần mềm tạI bất kỳ lúc nào.

0,25

đ

0,5đ

0,25đ

0,25đ

![Đề thi trắc nghiệm Kỹ thuật mạch điện tử: Tổng hợp [Năm]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/23481758356189.jpg)

![Đề thi học kì Kỹ thuật số năm 2014-2015 – Trường Đại học Bách Khoa TP.HCM [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250813/nhanmotchut_1/135x160/97661755077479.jpg)

![Bài giảng Nhập môn Kỹ thuật điện [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251208/nguyendoangiabao365@gmail.com/135x160/60591765176011.jpg)

![Bài giảng Cảm biến và ứng dụng: Chương 1 - Các khái niệm và đặc trưng cơ bản [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251204/kimphuong1001/135x160/51101764832169.jpg)